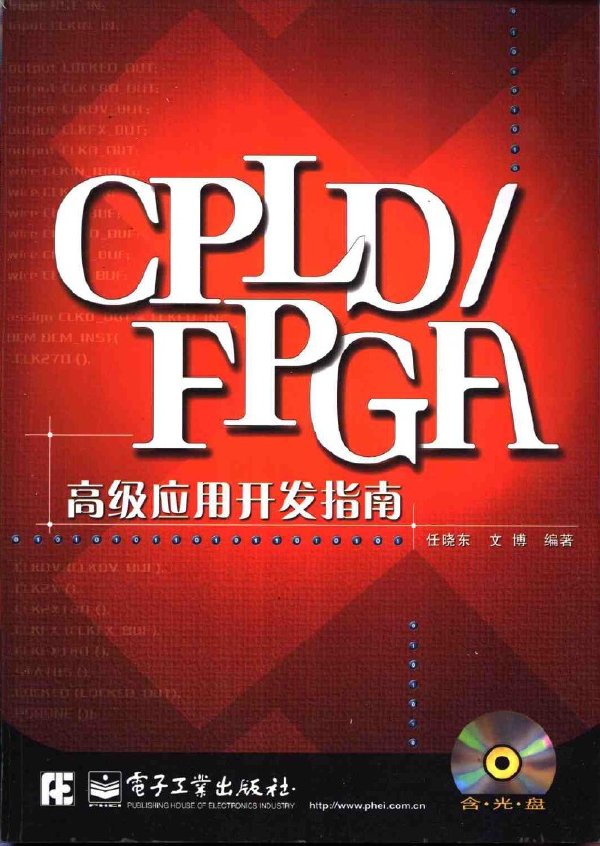

《CPLDFPGA高級應用開發指南》掃描版[PDF] 簡介: 中文名 : CPLDFPGA高級應用開發指南 作者 : 任曉東 文博 圖書分類 : 網絡 資源格式 : PDF 版本 : 掃描版 出版社 : 電子工業出版社 書號 : 7505387642 發行時間 : 2003年6月 地區 : 大陸 語言 : 簡體中文 簡介 : 內容簡介: 目前,CPLD/FPCA被廣泛地應用在航天、通信、醫療、工控等各個領域。本書從

"《CPLDFPGA高級應用開發指南》掃描版[PDF]"介紹

中文名: CPLDFPGA高級應用開發指南

作者: 任曉東

文博

圖書分類: 網絡

資源格式: PDF

版本: 掃描版

出版社: 電子工業出版社

書號: 7505387642

發行時間: 2003年6月

地區: 大陸

語言: 簡體中文

簡介:

內容簡介:

目前,CPLD/FPCA被廣泛地應用在航天、通信、醫療、工控等各個領域。本書從現代電子系統設計的角度出發,基於全球最大的可編程邏輯器件生產廠商Xilinx公司的系列產品,系統全面介紹了CPLD/FPCA的內部結構、設計流程和開發工具,詳細論述了CPLD/PPGA設計的時序約束、仿真驗證和綜合實現,重點介紹了嵌入PowerPC405的平台PPGA開發以及FPGA在DSP領域的最新應用。

對於從事各類電子系統設計的科研人員和應用技術工程師,本書是一本不可多得的針對電子系統原理和開發的參考書。本書也可作為有志於從事專用數字電路設計的高等院校高年級本科生和研究生的教學參考書。

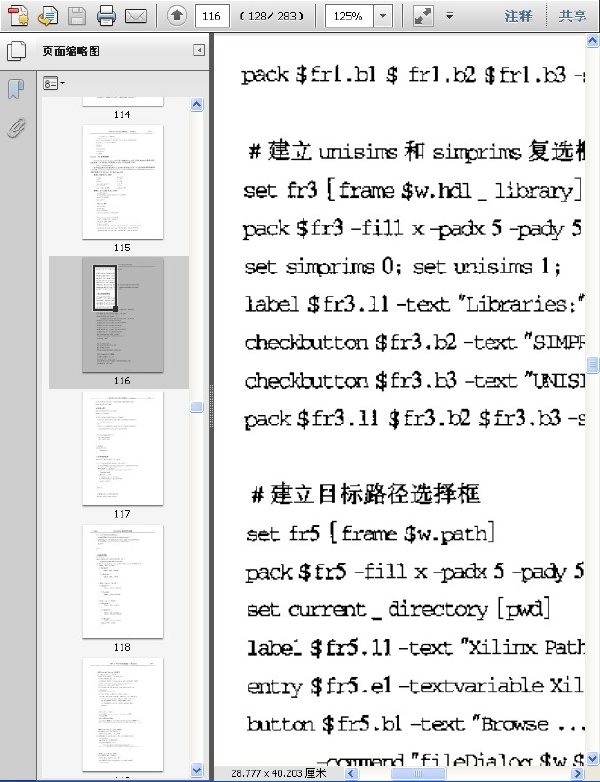

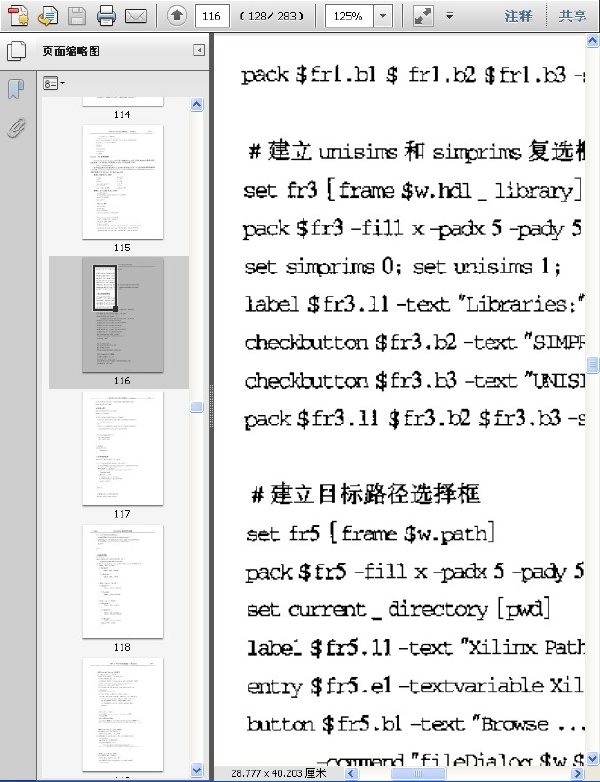

內容截圖:

目錄:

第1章 可編程邏輯器件與eda技術

1.1 可編程邏輯器件及其特征

1.1.1 簡單pld

1.1.2 cpld

1.1.3 fpca

1.1.4 門陣列

1.1.5 標准單元法

1.2 ppga的應用及設計要求

1.2.1 fpga的應用

1.2.2 fpga設計要求

1.3 eda技術簡介及軟件

1.3.1 eda技術

1.3.2 ppga開發用的軟件

1.4 因特網上的ppca及其他資源

1.5 小結

第2章 xilinx cpld系列產品

2.1 xc9500系列產品

2.1.1 簡介

2.1.2 器件結構

2.2 coolrunner-ii系列產品

. 2.2.1 簡介

2.2.2 器件結構

2.2.3 設計技巧

2.3 小結

第3章 xilinx fpga系列產品

3.1 spanan-iie系列產品

3.1.1 概述

3.1.2 器件結構

3.2 virtex-ii系列產品

3.2.1 概述

3.2.2 器件結構

3.3 virtex-iipro系列產品

3.3.1 概述

3.3.2 器件結構

3.4 小結

第4章 xilinx ise應用基礎

4.1 ise設計流程

4.1.1 設計輸入

4.1.2 功能仿真

4.1.3 綜合

4.1.4 實現

4.1.5 時序仿真

4.1.6 下載配置

4.2 ise基本設計工具

4.2.1 architecture wizard

4.2.2 pace

4.2.3 內核生成器(corecenerator)

4.2.4 impact

4.2.5 prom file formatter

4.3 小結

第5章 fpga高級設計技巧(一)——ise高級工具

5.1 f1oorplanner

5.1.1 概述

5.1.2 f100rplanner使用說明

5.2 fpca editor

5.2.1 概述

5.2.2 fpca editor使用說明

5.3 xpower

5.3.1 概述

5.3.2 xpower使用說明

5.4 chipscope

5.4.1 概述

5.4.2 chipscope使用說明

5.5 小結

第6章 fpga高級設計技巧(二)——約束與配置

6.1 約束設計

6.1.1 概述

6.1.2 時序約束

6.1.3 其他重要的約束參數

6.1.4 ucf文件和constrmntedjtor

6.2 配置設計

6.2.1 概述

6.2.2 下載配置模式

6.2.3 cpld下載配置設計

6.2.4 fpga下載配置設計

6.2.5 virtex-ii系列器件下載配置設計

6.3 小結

第7章 fpga高級設計技巧(三)——時鐘與ram

7.1 時鐘設計技巧

7.1.1 全局時鐘網絡

7.1.2 數字延遲鎖相環(dll)

7.1.3 數字時鐘管理器(dcm)

7.2 b1ockram設計技巧

7.2.1 b1cokram設計基礎

7.2.2 b1ockram設計說明

7.3 小結

第8章 fpga設計仿真驗證——modelsim

8.1 數字電路設計的仿真驗證

8.1.1 仿真驗證基本概念

8.1.2 testbench基本概念

8.1.3 teatbench設計提示

8.1.4 te8tbench設計示例

8.2 modelsim應用說明

8.2.1 modelsim基本命令

8.2.2 modelsim應用說明

8.3 小結

第9章 基於synplify的fpga綜合設計

9.1 synplify和synplify pro概述

9.1.1 選擇synplifypro的原因

9.1.2 ppga設計流程

9.1.3 synplifypro界面

9.2 synplifypro使用入門

9.2.1 建立一個工程

9.2.2 編譯

9.2.3 設置xilinx約束

9.2.4 設置與xilinx器件有關的選項

9.2.5 執行綜合

9.3 綜合報告的解析

9.4 時序修正

9.5 veriloghdl的設計風格

9.5.1 在編寫代碼之前的准備工作

9.5.2 可綜合的veriloghdl風格

9.5.3 veriloghdl代碼風格

9.5.4 程序員提示

9.6 小結

第10章 嵌入式系統的軟硬件設計

10.1 嵌入式系統的結構

10.1.1 cisc結構

10.1.2 risc結構

10.2 系統的軟硬件協同設計

10.3 設計重用與基於平台的設計

10.4 軟硬件協同設計的方法

10.5 以太網橋的設計實例

10.5.1 以lotos為基礎的協同設計

10.5.2 要設計的以太網橋

10.5.3 實例的具體分析

10.5.4 結果分析

10.6 小結

第11章 嵌入povverpc的平台fpga軟硬件設計

11.1 powerpc405內部結構和外部接口

11.1.1 powerpc405內部結構

11.1.2 powerpc405外部接口

11.2 edk應用說明

11.2.1 系統描述文件

11.2.2 edk開發流程

11.3 嵌入powerpc的平台fpga設計

11.3.1 嵌入powerpc的平台fpca設計

11.3.2 嵌入powerpc的平台ppca設計實例

11.4 小結

第12章 xilinxfpga在數字信號處理領域的應用

12.1 system generator基礎

12.1.1 系統級建模

12.1.2 dsp的設計流程

12.1.3 算術數據類型

12.1.4 硬件握手

12.1.5 按位和按周期對齊的建模

12.2 軟件使用基礎

12.2.1一般設計步驟

12.2.2 simulink系統周期與硬件時鐘頻率

12.2.3 同步機制

12.2.4 創建高性能設計的提示

12.2.5 logicore

12.2.6 自動創建的文件

12.3 積分的例子

12.3.1 simulink建模

12.3.2 vhdl等文件的生成

12.3.3 modelsim仿真

12.3.4 synplifypro綜合

12.3.5 翻譯、映射、布局布線

12.4 自編寫vhdl的例子

12.4.1 計數器的vhdl代碼

12.4.2 創建計數器的simulink仿真模型

12.4.3 計數器例子的文件

12.4.4 運行systemcenerator

12.4.5 計數器的仿真和綜合

12.5 自編寫veriloghdl的例子

12.5.1 計數器的veriloghdl代碼

12.5.2 創建計數器的simulink仿真模型

12.5.3 計數器例子的文件

12.5.4 運行systemcenerator

12.5.5 計數器的仿真和綜合

12.6 小結

附錄a ic和fpga設計新手必讀

a.1 引言

a.2 硬件描述語言的誕生及電子設計自動化工具的發展

a.3 各種eda工具介紹與自動化設計流程之關系

a.3.1 系統規范制定(dennespecification)

a.3.2 設計描述(design description)

a.3.3 功能驗證(function verification)

a.3.4 邏輯電路綜合(logic synthesis)

a.3.5 邏輯門級的電路功能驗證(gate-level netlist verification)

a.3.6 布局與布線(p1ace and routing)

a.3.7 布線後的電路功能驗證(post layout verification)

a.4 結論

附錄b verilog hdl與vhdl的比較

1.vhdl

2.verilog hdl

3.兩種語言的描述層次

4.1995年hdl的使用情況

5.vhdl與verilog hdl在各方面的比較

附錄c virtex-ii和spartan-ii的管腳

附錄d 實驗指導

實驗1 ise應用基礎

實驗目的

實驗內容

實驗說明

實驗步驟

實驗2 modelsim應用基礎

實驗目的

實驗內容

實驗說明

實驗步驟

實驗3 synplify的設計實例

實驗目的

實驗內容

實驗說明

實驗步驟

實驗4 基於powerpc405的fpca設計實例

實驗目的

實驗內容

實驗說明

實驗提示

實驗步驟

實驗5 systemgenerator的設計實例

實驗目的

實驗內容

實驗說明

積分實驗步驟

vhdl步驟

veriloghdl步驟

附錄e ic和fpga專業術語的中英文對照

附錄f xilinx fpga支持的ip列表

參考資料

作者: 任曉東

文博

圖書分類: 網絡

資源格式: PDF

版本: 掃描版

出版社: 電子工業出版社

書號: 7505387642

發行時間: 2003年6月

地區: 大陸

語言: 簡體中文

簡介:

內容簡介:

目前,CPLD/FPCA被廣泛地應用在航天、通信、醫療、工控等各個領域。本書從現代電子系統設計的角度出發,基於全球最大的可編程邏輯器件生產廠商Xilinx公司的系列產品,系統全面介紹了CPLD/FPCA的內部結構、設計流程和開發工具,詳細論述了CPLD/PPGA設計的時序約束、仿真驗證和綜合實現,重點介紹了嵌入PowerPC405的平台PPGA開發以及FPGA在DSP領域的最新應用。

對於從事各類電子系統設計的科研人員和應用技術工程師,本書是一本不可多得的針對電子系統原理和開發的參考書。本書也可作為有志於從事專用數字電路設計的高等院校高年級本科生和研究生的教學參考書。

內容截圖:

目錄:

第1章 可編程邏輯器件與eda技術

1.1 可編程邏輯器件及其特征

1.1.1 簡單pld

1.1.2 cpld

1.1.3 fpca

1.1.4 門陣列

1.1.5 標准單元法

1.2 ppga的應用及設計要求

1.2.1 fpga的應用

1.2.2 fpga設計要求

1.3 eda技術簡介及軟件

1.3.1 eda技術

1.3.2 ppga開發用的軟件

1.4 因特網上的ppca及其他資源

1.5 小結

第2章 xilinx cpld系列產品

2.1 xc9500系列產品

2.1.1 簡介

2.1.2 器件結構

2.2 coolrunner-ii系列產品

. 2.2.1 簡介

2.2.2 器件結構

2.2.3 設計技巧

2.3 小結

第3章 xilinx fpga系列產品

3.1 spanan-iie系列產品

3.1.1 概述

3.1.2 器件結構

3.2 virtex-ii系列產品

3.2.1 概述

3.2.2 器件結構

3.3 virtex-iipro系列產品

3.3.1 概述

3.3.2 器件結構

3.4 小結

第4章 xilinx ise應用基礎

4.1 ise設計流程

4.1.1 設計輸入

4.1.2 功能仿真

4.1.3 綜合

4.1.4 實現

4.1.5 時序仿真

4.1.6 下載配置

4.2 ise基本設計工具

4.2.1 architecture wizard

4.2.2 pace

4.2.3 內核生成器(corecenerator)

4.2.4 impact

4.2.5 prom file formatter

4.3 小結

第5章 fpga高級設計技巧(一)——ise高級工具

5.1 f1oorplanner

5.1.1 概述

5.1.2 f100rplanner使用說明

5.2 fpca editor

5.2.1 概述

5.2.2 fpca editor使用說明

5.3 xpower

5.3.1 概述

5.3.2 xpower使用說明

5.4 chipscope

5.4.1 概述

5.4.2 chipscope使用說明

5.5 小結

第6章 fpga高級設計技巧(二)——約束與配置

6.1 約束設計

6.1.1 概述

6.1.2 時序約束

6.1.3 其他重要的約束參數

6.1.4 ucf文件和constrmntedjtor

6.2 配置設計

6.2.1 概述

6.2.2 下載配置模式

6.2.3 cpld下載配置設計

6.2.4 fpga下載配置設計

6.2.5 virtex-ii系列器件下載配置設計

6.3 小結

第7章 fpga高級設計技巧(三)——時鐘與ram

7.1 時鐘設計技巧

7.1.1 全局時鐘網絡

7.1.2 數字延遲鎖相環(dll)

7.1.3 數字時鐘管理器(dcm)

7.2 b1ockram設計技巧

7.2.1 b1cokram設計基礎

7.2.2 b1ockram設計說明

7.3 小結

第8章 fpga設計仿真驗證——modelsim

8.1 數字電路設計的仿真驗證

8.1.1 仿真驗證基本概念

8.1.2 testbench基本概念

8.1.3 teatbench設計提示

8.1.4 te8tbench設計示例

8.2 modelsim應用說明

8.2.1 modelsim基本命令

8.2.2 modelsim應用說明

8.3 小結

第9章 基於synplify的fpga綜合設計

9.1 synplify和synplify pro概述

9.1.1 選擇synplifypro的原因

9.1.2 ppga設計流程

9.1.3 synplifypro界面

9.2 synplifypro使用入門

9.2.1 建立一個工程

9.2.2 編譯

9.2.3 設置xilinx約束

9.2.4 設置與xilinx器件有關的選項

9.2.5 執行綜合

9.3 綜合報告的解析

9.4 時序修正

9.5 veriloghdl的設計風格

9.5.1 在編寫代碼之前的准備工作

9.5.2 可綜合的veriloghdl風格

9.5.3 veriloghdl代碼風格

9.5.4 程序員提示

9.6 小結

第10章 嵌入式系統的軟硬件設計

10.1 嵌入式系統的結構

10.1.1 cisc結構

10.1.2 risc結構

10.2 系統的軟硬件協同設計

10.3 設計重用與基於平台的設計

10.4 軟硬件協同設計的方法

10.5 以太網橋的設計實例

10.5.1 以lotos為基礎的協同設計

10.5.2 要設計的以太網橋

10.5.3 實例的具體分析

10.5.4 結果分析

10.6 小結

第11章 嵌入povverpc的平台fpga軟硬件設計

11.1 powerpc405內部結構和外部接口

11.1.1 powerpc405內部結構

11.1.2 powerpc405外部接口

11.2 edk應用說明

11.2.1 系統描述文件

11.2.2 edk開發流程

11.3 嵌入powerpc的平台fpga設計

11.3.1 嵌入powerpc的平台fpca設計

11.3.2 嵌入powerpc的平台ppca設計實例

11.4 小結

第12章 xilinxfpga在數字信號處理領域的應用

12.1 system generator基礎

12.1.1 系統級建模

12.1.2 dsp的設計流程

12.1.3 算術數據類型

12.1.4 硬件握手

12.1.5 按位和按周期對齊的建模

12.2 軟件使用基礎

12.2.1一般設計步驟

12.2.2 simulink系統周期與硬件時鐘頻率

12.2.3 同步機制

12.2.4 創建高性能設計的提示

12.2.5 logicore

12.2.6 自動創建的文件

12.3 積分的例子

12.3.1 simulink建模

12.3.2 vhdl等文件的生成

12.3.3 modelsim仿真

12.3.4 synplifypro綜合

12.3.5 翻譯、映射、布局布線

12.4 自編寫vhdl的例子

12.4.1 計數器的vhdl代碼

12.4.2 創建計數器的simulink仿真模型

12.4.3 計數器例子的文件

12.4.4 運行systemcenerator

12.4.5 計數器的仿真和綜合

12.5 自編寫veriloghdl的例子

12.5.1 計數器的veriloghdl代碼

12.5.2 創建計數器的simulink仿真模型

12.5.3 計數器例子的文件

12.5.4 運行systemcenerator

12.5.5 計數器的仿真和綜合

12.6 小結

附錄a ic和fpga設計新手必讀

a.1 引言

a.2 硬件描述語言的誕生及電子設計自動化工具的發展

a.3 各種eda工具介紹與自動化設計流程之關系

a.3.1 系統規范制定(dennespecification)

a.3.2 設計描述(design description)

a.3.3 功能驗證(function verification)

a.3.4 邏輯電路綜合(logic synthesis)

a.3.5 邏輯門級的電路功能驗證(gate-level netlist verification)

a.3.6 布局與布線(p1ace and routing)

a.3.7 布線後的電路功能驗證(post layout verification)

a.4 結論

附錄b verilog hdl與vhdl的比較

1.vhdl

2.verilog hdl

3.兩種語言的描述層次

4.1995年hdl的使用情況

5.vhdl與verilog hdl在各方面的比較

附錄c virtex-ii和spartan-ii的管腳

附錄d 實驗指導

實驗1 ise應用基礎

實驗目的

實驗內容

實驗說明

實驗步驟

實驗2 modelsim應用基礎

實驗目的

實驗內容

實驗說明

實驗步驟

實驗3 synplify的設計實例

實驗目的

實驗內容

實驗說明

實驗步驟

實驗4 基於powerpc405的fpca設計實例

實驗目的

實驗內容

實驗說明

實驗提示

實驗步驟

實驗5 systemgenerator的設計實例

實驗目的

實驗內容

實驗說明

積分實驗步驟

vhdl步驟

veriloghdl步驟

附錄e ic和fpga專業術語的中英文對照

附錄f xilinx fpga支持的ip列表

參考資料

- 上一頁:《精通DirectX 3D圖形與動畫程序設計》(精通DirectX 3D圖形與動畫程序設計)掃描版[PDF]

- 下一頁:《DirectX高級動畫制作》(Advanced Animation with DirectX)掃描版[PDF]

相關資源:

- [經濟管理]《你也可以擁有一個億》掃描版[PDF]

- [人文社科]《霍元甲》(Legend of a fighter)國英雙語版[HALFCD]

- [其他圖書]遺失的世界 The Lost World 1999 第四季劇本

- [經濟管理]《新股民快速入門必讀:初入股市實戰技法全書》掃描版[PDF]

- [生活圖書]《太極拳講義》掃描版[PDF]

- [計算機與網絡]《Photoshop CS5 數碼照片處理268例》掃描版[PDF]

- [教育科技]《現代公關禮儀教程》掃描版[PDF]

- [計算機與網絡]《軟件開發實戰1200例:ASP.NET開發實戰1200例【附光盤】(第1卷)(第2卷)》掃描版[PDF]

- [人文社科]《程序的法理》(孫笑俠)掃描版[PDF]

- [其他圖書]《邏輯學導論(國外經典哲學教材譯叢)》(Introduction to Logic)((美)柯匹 & (美)科恩)影印[PDF]

- [教育科技]《《簡明微分幾何》》(《簡明微分幾何》)文字版

- [文學圖書]《江南草藥王》(甄銘)掃描版[PDF]

- [人文社科]《深奧的簡潔:從混沌,復雜到地球生命的起源

- [其他圖書]《廣告與招牌設計》

- [系統工具]《硬盤空間管理工具》(JAM Software SpaceObServer)v4.1.1.355/零售版[壓縮包]

- [教育科技]《最易犯錯的口語句型268例》掃描版[PDF]

- [其他資源綜合]《楚漢驕雄》(The Conquerors Story)TVB DVD(粵語/30集) 資料下載

- [生活百科]《海蒂性學報告:男人篇》掃描版[PDF] 資料下載

- [人文社科]《紅河》(Red River)[DVDRip]

- [硬盤游戲]《經典執政官》(Archon Classic)完整硬盤版[壓縮包]

- 《Python參考手冊 (第4版)》(Python Essential Reference

- 《平面設計材料表現與特殊效果》掃描版[PDF]

- 《TCP-IP詳解卷二:實現》(TCP/IP Illustrated, Vol 2: The Implementation)文字版[PDF]

- 《游戲音效編程》(Beginning Game Audio Programming)掃描版[PDF]

- 《SharePoint 2010 Web Parts 實戰》(SharePoint 2010 Web Parts in Action)英文文字版/更新源代碼[PDF]

- 《Windows Server 2003網絡專業指南》(戴有炜)掃描版[PDF]

- 《使用HTML&CSS正確構建自己的Web網站 》(Build Your Own Web Site The Right Way Using HTML & CSS)英文文字版/EPUB/更新第3版[PDF]

- 《DOS在磁盤管理與系統維護中的典型應用(入門篇)》掃描版[PDF]

- 《Ext JS 3.2 學習指南》(Learning Ext JS 3.2)英文文字版/更新源代碼[PDF]

- 《導師的解決方案手冊: 8088和8086微處理器編程》

- 《CG電視包裝制作揭秘》全彩掃描版[PDF]

- 《挖掘社交網絡》(Mining the Social Web: Analyzing Dat

免責聲明:本網站內容收集於互聯網,本站不承擔任何由於內容的合法性及健康性所引起的爭議和法律責任。如果侵犯了你的權益,請通知我們,我們會及時刪除相關內容,謝謝合作! 聯系信箱:[email protected]

Copyright © 電驢下載基地 All Rights Reserved