| 《PCI Express系統體系結構標准教材》(PCI Express System Architecture)掃描版[PDF] | |

|---|---|

| 下載分級 | 图书资源 |

| 資源類別 | 計算機與網絡 |

| 發布時間 | 2017/7/10 |

| 大 小 | - |

《PCI Express系統體系結構標准教材》(PCI Express System Architecture)掃描版[PDF] 簡介: 中文名 : PCI Express系統體系結構標准教材 原名 : PCI Express System Architecture 作者 : (美)Pavi Budruk Don Anderson Tom Shanley 譯者 : 田玉敏 王崧 張波 圖書分類 : 硬件 資源格式 : PDF 版本 : 掃描版 出版社 : 電子工業出版社 書號 : 7121017946 發行

電驢資源下載/磁力鏈接資源下載:

- 下載位址: [www.ed2k.online][PCI.EXPRESS系統體系結構標准教材].(美)Pavi.Budruk,Don.Anderson,Tom.Shanley.掃描版.pdf

- 下載位址: [www.ed2k.online]PCI.Express.System.Architecture.chm

- 下載位址: [www.ed2k.online]Addison-wesley,.pci.express.system.architecture.-2003-.lib.chm

全選

"《PCI Express系統體系結構標准教材》(PCI Express System Architecture)掃描版[PDF]"介紹

中文名: PCI Express系統體系結構標准教材

原名: PCI Express System Architecture

作者: (美)Pavi Budruk

Don Anderson

Tom Shanley

譯者: 田玉敏

王崧

張波

圖書分類: 硬件

資源格式: PDF

版本: 掃描版

出版社: 電子工業出版社

書號: 7121017946

發行時間: 2005年11月

地區: 大陸

語言: 簡體中文

簡介:

內容介紹:

本書首先概述第三代pci express總線和第二代總線及其之間的關系和區別,然後全面論述目前市場上最為流行的第三代總線——ci express。主要內容包括:pci express總線的發展過程和特點;pci express總線事務路由方法;數據包傳送的主要協議和實現服務質量的方法;事務順序、中斷與錯務處理;pci express總線物理層詳述;復位和鏈路定向與初始化;附加卡的外觀結構;pci express的電源管理;pci express配置方式。附錄提供的內容包括pci express的測試、調試和驗證。

本書詳細描述的pci express系統的體系結構,以及列舉的大量示例,對於理解pci express內容並構思其用途有很大幫助,是軟硬件設計人員和技術人員不可多得的參考書籍。

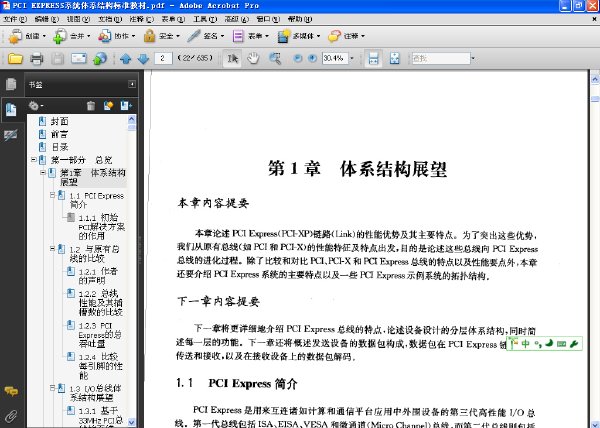

內容截圖:

目錄:

第一部分 總 覽

第1章 體系結構展望

1.1 pci express簡介

1.1.1 初始pci解決方案的作用

1.2 與原有總線的比較

1.2.1 作者的聲明

1.2.2 總線性能及其插槽數的比較

1.2.3 pci express的總吞吐量

1.2.4 比較每引腳的性能

1.3 i/o總線體系結構展望

1.3.1 基於33mhz pci總線的系統

1.3.2 基於66mhz pci總線的系統

1.3.3 基於66mhz和133mhz pci-x 1.0總線的平台

1.3.4 基於ddr和qdr pci-x 2.0總線的平台

1.4 pci express的線路

1.4.1 pci express的拓撲結構

1.4.2 pci express系統模塊圖

1.5 pci express規范

第2章 體系結構概述

2.1 pci express事務簡介

.2.1.1 pci express事務協議

2.1.2一些事務示例

2.2 pci express的設備層

2.2.1 概述

2.2.2 設備層及相關的數據包

2.2.3 各pci express設備層的功能

2.3 非報告存儲器讀事務示例

2.4 熱插拔

2.5 pci express的性能與數據傳送效率

第二部分 事務協議

第3章 地址空間與事務路由

3.1 簡介

3.1.1 接收器檢查3種類型的鏈路流量

3.1.2 多端口設備承擔路由負荷

3.1.3 端點的路由能力有限

3.1.4 系統路由策略是可編程的

3.2 兩種類型的本地鏈路流量

3.2.1 有序集

3.2.2 數據鏈路層數據包(dllp)

3.3 處理層數據包路由基礎

3.3.1 用於訪問4種地址空間的tlp

3.3.2 使用分離事務協議了嗎

3.3.3 tlp路由的3種方法

3.3.4 pci express的路由方法與pci兼容嗎

3.3.5 定義數據包格式和路由的頭字段

3.3.6 使用tlp的頭信息:概述

3.4 應用路由機制

3.4.1 地址路由

3.4.2 id路由

3.4.3 隱式路由

3.5 路由選項的即插即用設置

3.5.1 路由配置是pci兼容的嗎

3.5.2 基址寄存器(bar):類型o、類型1的頭

3.5.3 基址/限界寄存器,只限類型1頭

3.5.4 總線號寄存器,只限類型1頭

第4章 基於數據包的事務

4.1 基於數據包的協議簡介

4.1.1 為什麼要使用基於數據包的事務協議

4.2 處理層數據包

4.2.1 組裝和拆解tlp

4.2.2 設備核心請求訪問4種空間

4.2.3 所定義的tlp事務變體

4.2.4 tlp的結構

4.2.5 建立事務:tlp請求和完成

4.3 數據鏈路層數據包

4.3.1 dllp的類型

4.3.2 dllp是本地流量

4.3.3 接收器對dllp的處理

4.3.4 發送一個數據鏈路層數據包

4.3.5 dllp數據包的類型

第5章 ack/nak協議

5.1 通過各鏈路可靠地傳輸tlp

5.2 ack/nak協議的基本組成

5.2.1 ack/nak協議中發送器的基本組成

5.2.2 ack/nak協議的接收器基本組成

5.3 ack/nak dllp的格式

5.4 ack/nak協議詳解

5.4.1 發送器協議詳解

5.4.2 接收器協議詳解

5.5 利用ack/nak協議可靠地處理錯誤情況

5.6 ack/nak協議小結

5.6.1 發送器部分

5.6.2 接收器部分

5.7 安排數據包時推薦的優先級

5.8 更多的示例

5.8.1 丟失tlp

5.8.2 丟失ack dllp或ack dllp並有crc錯誤

5.8.3 丟失跟隨nak dllp的ack dllp

5.9 交換器直通轉發模式

5.9.1 沒有直通轉發模式

5.9.2 交換器直通轉發模式

第6章 qos/xc/vc和仲裁

6.1 服務質量

6.1.1 同步事務支持

6.1.2 差異性服務

6.2 對qos/tc/vc和仲裁的看法

6.3 流量類別和虛擬通道

6.3.1 vc分配和tc映射

6.4 仲裁

6.4.1 虛擬信道仲裁

6.4.2 端口仲裁

6.4.3 交換器仲裁示例

第7章 流控制

7.1 流控制的概念

7.2 流控制緩沖區

7.2.1 vc流控制緩沖區的組織

7.2.2 流控制信用

7.2.3 流控制緩沖區的最大容量

7.3 流控制機制簡介

7.3.1 流控制的基本組成

7.4 流控制數據包

7.5 流控制模型的操作——示例

7.5.1 第一階段——初始化之後的流控制

7.5.2 第二階段——流控制緩沖區填滿

7.5.3 第三階段——信用限額計數器翻轉

7.5.4 第四階段——fc緩沖區溢出錯誤檢查

7.6 通告無限流控制

7.6.1 誰能通告無限流控制信用

7.6.2 無限信用通告的特殊用途

7.6.3 頭和數據通告可能沖突

7.7 最小流控制通告

7.8 流控制初始化

7.8.1 fc初始化序列

7.9 fc.init之後的流控制更新

7.9.1 fc-update dllp的格式和內容

7.9.2 流控制更新頻率

7.9.3 錯誤檢測定時器——一種偽需求

第8章 事務順序

8.1 簡介

8.2 生產者/使用者模型

8.3 真正的pci express順序規則

8.3.1 真正pci express設備的生產者/使用者模型

8.4 靈活的順序

8.4.1 ro對存儲器寫和消息的影響

8.4.2 ro對存儲器讀事務的影響

8.4.3 強順序規則總結

8.5 改變順序規則,提高性能

8.5.1 強順序可能導致事務阻塞

8.5.2 用vc緩沖區完成的順序管理

8.5.3 改進的順序規則小結

8.6 支持pci總線和避免死鎖

第9章 中斷

9.1 發送中斷的兩種方法

9.2 消息信號中斷

9.2.1 msi功能寄存器組

9.2.2 msi配置基礎

9.2.3 生成msi中斷請求的基礎

9.2.4 中斷處理程序處理時的存儲器同步

9.2.5 中斷延遲

9.2.6 一些規則、建議等等

9.3 傳統的pci中斷發送機制

9.3.1 背景知識——pci中斷信令

9.3.2 虛擬intx信令

9.4 設備可以同時支持msi和傳統的中斷

9.5 基本系統外圍設備必須考慮的特殊情況

9.5.1 示例系統

第10章 錯誤檢測和處理

10.1 背景

10.2 pci express錯誤管理簡介

10.2.1 pci express的錯誤校驗機制

10.2.2 錯誤報告機制

10.2.3 錯誤處理機制

10.3 pci express錯誤的來源

10.3.1 ecrc的產生與校驗

10.3.2 數據中毒(可選)

10.3.3 tc到vc映射錯誤

10.3.4 鏈路流控制相關的錯誤

10.3.5 畸形處理層數據包(tlp)

10.3.6 分離事務的錯誤

10.4 錯誤分類

10.4.1 可修正的錯誤

lo.4.2 不可修正的非致命錯誤

10.4.3不可修正的致命錯誤

10.5 報告錯誤的方法

10.5.1 錯誤消息

10.5.2 完成狀況

10.6 基本的錯誤檢測和處理

10.6.1 pci兼容的錯誤報告機制

10.6.2 pci express的基本錯誤處理

10.7 高級錯誤報告機制

10.7.1 ecrc的生成和校驗

10.7.2 粘滯比特的處理

10.7.3 高級可修正錯誤的處理

10.7.4 高級不可修正錯誤的處理

10.7.5 錯誤記錄

10.7.6 根聯合體錯誤跟蹤和報告

10.8 錯誤記錄與報告小結

第三部 分物理層

第11章 物理層邏輯

11.1 物理層概述

11.1.1 聲明

11.1.2 發送邏輯概述

11.1.3 接收邏輯概述

11.1.4 物理層鏈路活動狀態電源管理

11.1.5 鏈路定向和初始化

11.2 發送邏輯細節

11.2.1 發送(tx)緩沖區

11.2.2 多路復用器(mux)和多路復用器控制邏輯

11.2.3 字節拆分(可選)

11.2.4 擾頻器

11.2.5 8b/10b編碼

11.2.6 並行到串行轉換器(串行器)

11.2.7 差動發送驅動器

11.2.8 發送器(tx)時鐘

11.2.9 發送邏輯的其他主題

11.3 接收邏輯的細節

11.3.1 差動接收器

11.3.2 接收時鐘的恢復

11.3.3 串行到並行轉換器(反串行器)

11.3.4 符號邊界測定(符號鎖定)

11.3.5 接收器時鐘補償邏輯

11.3.6 通道到通道的相位補償

11.3.7 8b/10b解碼器

11.3.8 去擾頻器

11.3.9 字節反拆分

11.3.10 過濾器和數據包校正檢查

11.3.11 接收緩沖區(rx緩沖區)

11.4 物理層錯誤處理

第12章 電氣物理層

12.1 電氣物理層概述

12.2 高速電氣信令

12.2.1 時鐘要求

12.2.2 阻抗和終結

12.2.3 13(3共模電壓

12.2.4 esd和短路要求

12.2.5 接收器檢測

12.2.6 差動驅動器和接收器

12.2.7 電氣空閒

12.2.8 鏈路上發送線路的損耗

12.2.9 ac耦合

12.2.10 去矯(或預矯)

12.2.11 信標信令

12.3 lvds眼圖

12.3.1 抖動、噪音和信號衰減

12.3.2 眼測試(eye test)

12.3.3 最優眼

12.3.4 抖動可使眼邊加寬或變窄

12.3.5 噪音和信號衰減使眼變高

12.4 發送器驅動器特性

12.4.1 概述

12.4.2 發送驅動器一致性測試和測量負載

12.5 輸入接收器的特性

12.6 在各種電源狀態中的電氣物理層狀態

第13章 系統復位

13.1 兩類系統復位

13.1.1 基本復位

13.1.2 帶內復位或hot復位

13.2 退出復位

13.3 從l2低功率狀態中的鏈路喚醒

第14章 鏈路初始化和定向

14.1 鏈路初始化和定向概述

14.1.1 概述

14.2 鏈路定向和初始化期間所用的有序集

14.2.1 ts1和ts2有序集

14.2.2 電氣空閒有序集

14.2.3 fts有序集

14.2.4 skip有序集

14.3 鏈路定向和狀況狀態機(ltssm)

14.3.1 概述

14.3.2 ltssm各狀態概述

14.4 ltssm各狀態詳述

14.4.1 檢測狀態

14.4.2 輪詢狀態

14.4.3 配置狀態

14.4.4 恢復狀態

14.4.5 lo狀態

14.4.6 los狀態

14.4.7 l1狀態

14.4.8 l2狀態

14.4.9 hot復位狀態

14.4.10 禁用狀態

14.4.11 回環狀態

14.5 與ltssm相關的配置寄存器

14.5.1 鏈路功能寄存器

14.5.2 鏈路狀況寄存器

14.5.3 鏈路控制寄存器

第四部分 與電源有關的主題

第15章 功率預算

15.1 功率預算簡介

15.2 功率預算的各個要素

15.3 插槽功率極限控制

15.3.1 擴充端口的插槽功率極限

15.3.2 擴充設備限制功率消耗

15.4 功率預算功能寄存器組

第16章 電源管理

16.1 簡介

16.2 配置軟件的入門知識

16.2.1 pci pm基礎

16.2.2 onnow design initiative計劃定義了全部pm

16.2.3 pci express電源管理與acpi

16.3 設備功能的電源管理

16.3.1 pm功能寄存器組

16.3.2 設備的pm狀態

16.3.3 pci-pm寄存器詳述

16.4 鏈路電源管理簡介

16.5 鏈路活動狀態電源管理

16.5.1 los狀態

16.5.2 l1 aspm狀態

16.5.3 aspm退出延遲

16.6 軟件發起的鏈路電源管理

16.6.1 d1/d2/d3hot和l1狀態

16.6.2 l2/l3准備就緒——切斷鏈路的電源

16.7 鏈路喚醒協議和pme的生成

16.7.1 pme消息

16.7.2 pme序列

16.7.3 避免pme消息產生背壓(back pressure)死鎖

16.7.4 pme環境

16.7.5 喚醒無法通信的鏈路

16.7.6 輔助電源

第五部分 可選功能

第17章 熱插拔

17.1 背景

17.2 pci express環境下的熱插拔

17.2.1 突然移除通知

17.2.2 pci熱插拔和pci express熱插拔的區別

17.3 支持熱插拔所需的基本要素

17.3.1 軟件基本要素

17.3.2 硬件基本要素

17.4 卡移除與插人過程

17.4.1開與關狀態

17.4.2卡移除過程

17.4.3卡插入過程

17.5 標准使用模型

17.5.1 背景

17.5.2 標准用戶接口

17.6 標准熱插拔控制器信令接口

17.7 熱插拔控制器編程接口

17.7.1 插槽功能

17.7.2 插槽控制

17.7.3 插槽狀況和事件管理

17.7.4 卡插槽與服務器10模塊實現

17.8 插槽編號

17.8.1 物理插槽id

17.9 終止卡與驅動程序的活動

17.9.1 概述

17.9.2 驅動程序暫停(可選)

17.10 原語

第18章 附加卡與連接器

18.1 簡介

18.1.1 附加卡連接器

18.1.2 輔助信號

18.1.3 電氣要求

18.1.4 附加卡的互操作性

18.2 正在開發的外形規格

18.2.1 概述

18.2.2 服務器10模塊(siom)

18.2.3 提升卡

18.2.4 微型pci express卡

18.2.5 newcard外形規格

第六部分 pci express配置

第19章 配置概述

19.1 設備與功能的定義

19.2 主總線與二級總線的定義

19.3 系統啟動時拓撲未知

19.4 每種功能實現一組配置寄存器

19.4.1 簡介

19.4.2 功能配置空間

19.5 主機/pci橋的配置寄存器

19.6 由處理器發起的配置事務

19.6.1 僅根聯合體能發起配置事務

19.6.2 配置事務僅能向下游移動

19.6.3 沒有對等配置事務

19.7 配置事務通過總線、設備和功能號路由

19.8 如何發現功能

19.9 如何區分pci到pci橋與非橋功能

第20章 配置機制

20.1 簡介

20.2 pci兼容配置機制

20.2.1 背景

20.2.2 pci兼容配置機制說明

20.3 pci express增強配置機制

20.3.1 說明

20.3.2 規則

20.4 類型0配置請求

20.5 類型1配置請求

20.6 pci兼容配置訪問示例

20.7 增強配置訪問示例

20.8 初始配置訪問

20.8.1 初始化期間會發生什麼

20.8.2 pci中初始化階段的定義

20.8.3 pci-x中初始化階段的定義

20.8.4 pci express與初始化時間

20.8.5 運行期間對crs接收的rc響應

第21章 pci express枚舉

21.1 簡介

21.2 帶單個根聯合體系統的枚舉

21.3 枚舉帶多個根聯合體的系統

21.3.1 pci兼容配置機制的運行特征

21.3.2 增強配置機制的運行特征

21.3.3 枚舉過程

21.4 根聯合體或交換器內的多功能設備

21.4.1 根聯合體內的多功能設備

21.4.2 交換器內的多功能設備

21.5 嵌入交換器或根聯合體中的端點

21.6 記住你的身份

21.6.1 概述

21.6.2 根聯合體總線號/設備號的分配

21.6.3 在id分配前發起請求

21.6.4 在id分配前發起完成

21.7 根聯合體寄存器塊(rcrb)

21.7.1 rcrb地址中的問題

21.7.2 有關rcrb的其他信息

21.8 其他規則

21.8.1 分割配置事務要求單個完成

21.8.2 pci express到pci橋或pci express到pci-x橋的問題

21.8.3 pci特殊周期事務

第22章 pci兼容配置寄存器

22.1 頭類型0(header type 0)

22.1.1 概述

22.1.2 兼容pci的頭類型o寄存器

22.1.3 與pci不兼容的頭類型o寄存器

22.1.4 用於識別設備驅動程序的寄存器

22.1.5 頭類型寄存器

22.1.6 bist寄存器

22.1.7 功能指針寄存器

22.1.8 cardbus cis指針寄存器

22.1.9 擴展rom基址寄存器

22.1.10 命令寄存器

22.1.11 狀況寄存器

22.1.12 緩存行大小寄存器

22.1.13 主控器延時定時器寄存器

22.1.14 中斷線寄存器

22.1.15 中斷引腳寄存器

22.1.16 基址寄存器

22.1.17 min_gnt/max_lat寄存器

22.2 頭類型1(header type 1)

22.2.1 概述

22.2.2 兼容pci的頭類型1奇存器

22.2.3 與pci不兼容的頭類型1寄存器

22.2.4 術語

22.2.5 總線號寄存器

22.2.6 廠商id寄存器

22.2.7 設備id寄存器

22.2.8 修訂版id寄存器

22.2.9 類代碼寄存器

22.2.10 頭類型寄存器

22.2.11 bist寄存器

22.2.12 功能指針寄存器

22.2.13 基本事務過濾機制

22.2.14 橋的存儲器、寄存器組和設備rom

22.2.15 橋的io過濾器

22.2.16 橋的可預取存儲器過濾器

22.2.17 橋的存儲器映射io過濾器

22.2.18 橋命令寄存器

22.2.19 橋狀況寄存器

22.2.20 橋高速緩存行大小寄存器

22.2.21 橋延遲定時器寄存器

22.2.22 與橋中斷有關的寄存器

22.3 pci兼容功能

22.3.1 agp功能

22.3.2 關鍵產品數據(vpd)功能

22.3.3 機箱/插槽編號寄存器簡介

22.3.4 機箱與插槽號的分配

第23章 擴展rom

23.1 rom的作用——可在啟動期間使用的設備

23.2 rom檢測

23.3 必需的rom映射

23.4 rom的內容

23.4.1多代碼映像

23.4.2 代碼映像的格式

23.5 初始化代碼的執行

23.6 開放固件簡介

23.6.1 概述

23.6.2 通用設備驅動程序的格式

23.6.3 傳遞資源列表到即插即用os

第24章 express專用配置寄存器

24.1 簡介

24.2 pci express功能寄存器組

24.2.1 簡介

24.2.2 必需的寄存器

24.2.3 插槽寄存器

24.2.4 根端口寄存器

24.3 pci express擴展功能

24.3.1 概述

24.3.2 高級錯誤報告功能

24.3.3 虛擬信道(vc)功能

24.3.4 設備序列號功能寄存器組

24.3.5 功率預算功能寄存器組

24.4 rcrb

24.4.1 概述

24.4.2 固件向os提供每個rcrb的基地址

24.4.3 對rcrb的不對齊或鎖定訪問

24.4.4 rcrb中的擴展功能寄存器組

24.4.5 rcrb丟失鏈路

附錄a 測試、調試和驗證

a.1 目的

a.2 串行總線的拓撲結構

a.3 雙單工

a.4 設置分析儀、捕獲和觸發條件

a.5 鏈路定向,通信的第一步

a.6 插槽連接器與mid-bus墊

a.7 練習:深入的驗證

a.8 信號完整性、設計和測量

a.8.1 概述

a.8.2 高速pcb的設計要求

附錄b pci express體系結構的市場及應用

b.1 簡介

b.2 企業計算系統

b.2.1 桌面系統

b.2.2 服務器系統

b.2.3 嵌入式控制系統

b.2.4 存儲系統

b.2.5 通信系統

b.3 小結

附錄c 用pci express技術實現智能適配器和多主機系統

c.1 簡介

c.2 使用模型

c.2.1 智能適配器

c.2.2 主機故障轉移

c.2.3 多處理器系統

c.3 使用pci的多處理器實現歷史

c.4 在pci express基本系統中實現多主機/智能適配器

c.4.1 示例:在pci express基本系統中實現智能適配器

c.4.2 示例:在pci express系統中實現故障轉移

c.4.3 示例:在pci express基本系統中實現雙主機

c.5 小結

c.6 地址轉換

c.6.1 直接地址轉換

c.6.2 基於查找表的地址轉換

c.6.3 下游bar限界寄存器

c.6.4 轉發64位地址的存儲器事務

附錄d 類代碼

附錄e 鎖定事務系列

e.1 簡介

e.2 背景

e.3 pci express鎖定協議

e.3.1 鎖定消息——虛擬鎖定信號

e.3.2 鎖定協議序列——一個示例

e.4 鎖定規則小結

e.4.1 與鎖定事務的發起和傳播有關的規則

e.4.2 與交換器有關的規則

e.4.3 與pci express/pci橋有關的規則

e.4.4 與根聯合體有關的規則

e.4.5 與傳統端點有關的規則

e.4.6 與pci express端點有關的規則

原名: PCI Express System Architecture

作者: (美)Pavi Budruk

Don Anderson

Tom Shanley

譯者: 田玉敏

王崧

張波

圖書分類: 硬件

資源格式: PDF

版本: 掃描版

出版社: 電子工業出版社

書號: 7121017946

發行時間: 2005年11月

地區: 大陸

語言: 簡體中文

簡介:

內容介紹:

本書首先概述第三代pci express總線和第二代總線及其之間的關系和區別,然後全面論述目前市場上最為流行的第三代總線——ci express。主要內容包括:pci express總線的發展過程和特點;pci express總線事務路由方法;數據包傳送的主要協議和實現服務質量的方法;事務順序、中斷與錯務處理;pci express總線物理層詳述;復位和鏈路定向與初始化;附加卡的外觀結構;pci express的電源管理;pci express配置方式。附錄提供的內容包括pci express的測試、調試和驗證。

本書詳細描述的pci express系統的體系結構,以及列舉的大量示例,對於理解pci express內容並構思其用途有很大幫助,是軟硬件設計人員和技術人員不可多得的參考書籍。

內容截圖:

目錄:

第一部分 總 覽

第1章 體系結構展望

1.1 pci express簡介

1.1.1 初始pci解決方案的作用

1.2 與原有總線的比較

1.2.1 作者的聲明

1.2.2 總線性能及其插槽數的比較

1.2.3 pci express的總吞吐量

1.2.4 比較每引腳的性能

1.3 i/o總線體系結構展望

1.3.1 基於33mhz pci總線的系統

1.3.2 基於66mhz pci總線的系統

1.3.3 基於66mhz和133mhz pci-x 1.0總線的平台

1.3.4 基於ddr和qdr pci-x 2.0總線的平台

1.4 pci express的線路

1.4.1 pci express的拓撲結構

1.4.2 pci express系統模塊圖

1.5 pci express規范

第2章 體系結構概述

2.1 pci express事務簡介

.2.1.1 pci express事務協議

2.1.2一些事務示例

2.2 pci express的設備層

2.2.1 概述

2.2.2 設備層及相關的數據包

2.2.3 各pci express設備層的功能

2.3 非報告存儲器讀事務示例

2.4 熱插拔

2.5 pci express的性能與數據傳送效率

第二部分 事務協議

第3章 地址空間與事務路由

3.1 簡介

3.1.1 接收器檢查3種類型的鏈路流量

3.1.2 多端口設備承擔路由負荷

3.1.3 端點的路由能力有限

3.1.4 系統路由策略是可編程的

3.2 兩種類型的本地鏈路流量

3.2.1 有序集

3.2.2 數據鏈路層數據包(dllp)

3.3 處理層數據包路由基礎

3.3.1 用於訪問4種地址空間的tlp

3.3.2 使用分離事務協議了嗎

3.3.3 tlp路由的3種方法

3.3.4 pci express的路由方法與pci兼容嗎

3.3.5 定義數據包格式和路由的頭字段

3.3.6 使用tlp的頭信息:概述

3.4 應用路由機制

3.4.1 地址路由

3.4.2 id路由

3.4.3 隱式路由

3.5 路由選項的即插即用設置

3.5.1 路由配置是pci兼容的嗎

3.5.2 基址寄存器(bar):類型o、類型1的頭

3.5.3 基址/限界寄存器,只限類型1頭

3.5.4 總線號寄存器,只限類型1頭

第4章 基於數據包的事務

4.1 基於數據包的協議簡介

4.1.1 為什麼要使用基於數據包的事務協議

4.2 處理層數據包

4.2.1 組裝和拆解tlp

4.2.2 設備核心請求訪問4種空間

4.2.3 所定義的tlp事務變體

4.2.4 tlp的結構

4.2.5 建立事務:tlp請求和完成

4.3 數據鏈路層數據包

4.3.1 dllp的類型

4.3.2 dllp是本地流量

4.3.3 接收器對dllp的處理

4.3.4 發送一個數據鏈路層數據包

4.3.5 dllp數據包的類型

第5章 ack/nak協議

5.1 通過各鏈路可靠地傳輸tlp

5.2 ack/nak協議的基本組成

5.2.1 ack/nak協議中發送器的基本組成

5.2.2 ack/nak協議的接收器基本組成

5.3 ack/nak dllp的格式

5.4 ack/nak協議詳解

5.4.1 發送器協議詳解

5.4.2 接收器協議詳解

5.5 利用ack/nak協議可靠地處理錯誤情況

5.6 ack/nak協議小結

5.6.1 發送器部分

5.6.2 接收器部分

5.7 安排數據包時推薦的優先級

5.8 更多的示例

5.8.1 丟失tlp

5.8.2 丟失ack dllp或ack dllp並有crc錯誤

5.8.3 丟失跟隨nak dllp的ack dllp

5.9 交換器直通轉發模式

5.9.1 沒有直通轉發模式

5.9.2 交換器直通轉發模式

第6章 qos/xc/vc和仲裁

6.1 服務質量

6.1.1 同步事務支持

6.1.2 差異性服務

6.2 對qos/tc/vc和仲裁的看法

6.3 流量類別和虛擬通道

6.3.1 vc分配和tc映射

6.4 仲裁

6.4.1 虛擬信道仲裁

6.4.2 端口仲裁

6.4.3 交換器仲裁示例

第7章 流控制

7.1 流控制的概念

7.2 流控制緩沖區

7.2.1 vc流控制緩沖區的組織

7.2.2 流控制信用

7.2.3 流控制緩沖區的最大容量

7.3 流控制機制簡介

7.3.1 流控制的基本組成

7.4 流控制數據包

7.5 流控制模型的操作——示例

7.5.1 第一階段——初始化之後的流控制

7.5.2 第二階段——流控制緩沖區填滿

7.5.3 第三階段——信用限額計數器翻轉

7.5.4 第四階段——fc緩沖區溢出錯誤檢查

7.6 通告無限流控制

7.6.1 誰能通告無限流控制信用

7.6.2 無限信用通告的特殊用途

7.6.3 頭和數據通告可能沖突

7.7 最小流控制通告

7.8 流控制初始化

7.8.1 fc初始化序列

7.9 fc.init之後的流控制更新

7.9.1 fc-update dllp的格式和內容

7.9.2 流控制更新頻率

7.9.3 錯誤檢測定時器——一種偽需求

第8章 事務順序

8.1 簡介

8.2 生產者/使用者模型

8.3 真正的pci express順序規則

8.3.1 真正pci express設備的生產者/使用者模型

8.4 靈活的順序

8.4.1 ro對存儲器寫和消息的影響

8.4.2 ro對存儲器讀事務的影響

8.4.3 強順序規則總結

8.5 改變順序規則,提高性能

8.5.1 強順序可能導致事務阻塞

8.5.2 用vc緩沖區完成的順序管理

8.5.3 改進的順序規則小結

8.6 支持pci總線和避免死鎖

第9章 中斷

9.1 發送中斷的兩種方法

9.2 消息信號中斷

9.2.1 msi功能寄存器組

9.2.2 msi配置基礎

9.2.3 生成msi中斷請求的基礎

9.2.4 中斷處理程序處理時的存儲器同步

9.2.5 中斷延遲

9.2.6 一些規則、建議等等

9.3 傳統的pci中斷發送機制

9.3.1 背景知識——pci中斷信令

9.3.2 虛擬intx信令

9.4 設備可以同時支持msi和傳統的中斷

9.5 基本系統外圍設備必須考慮的特殊情況

9.5.1 示例系統

第10章 錯誤檢測和處理

10.1 背景

10.2 pci express錯誤管理簡介

10.2.1 pci express的錯誤校驗機制

10.2.2 錯誤報告機制

10.2.3 錯誤處理機制

10.3 pci express錯誤的來源

10.3.1 ecrc的產生與校驗

10.3.2 數據中毒(可選)

10.3.3 tc到vc映射錯誤

10.3.4 鏈路流控制相關的錯誤

10.3.5 畸形處理層數據包(tlp)

10.3.6 分離事務的錯誤

10.4 錯誤分類

10.4.1 可修正的錯誤

lo.4.2 不可修正的非致命錯誤

10.4.3不可修正的致命錯誤

10.5 報告錯誤的方法

10.5.1 錯誤消息

10.5.2 完成狀況

10.6 基本的錯誤檢測和處理

10.6.1 pci兼容的錯誤報告機制

10.6.2 pci express的基本錯誤處理

10.7 高級錯誤報告機制

10.7.1 ecrc的生成和校驗

10.7.2 粘滯比特的處理

10.7.3 高級可修正錯誤的處理

10.7.4 高級不可修正錯誤的處理

10.7.5 錯誤記錄

10.7.6 根聯合體錯誤跟蹤和報告

10.8 錯誤記錄與報告小結

第三部 分物理層

第11章 物理層邏輯

11.1 物理層概述

11.1.1 聲明

11.1.2 發送邏輯概述

11.1.3 接收邏輯概述

11.1.4 物理層鏈路活動狀態電源管理

11.1.5 鏈路定向和初始化

11.2 發送邏輯細節

11.2.1 發送(tx)緩沖區

11.2.2 多路復用器(mux)和多路復用器控制邏輯

11.2.3 字節拆分(可選)

11.2.4 擾頻器

11.2.5 8b/10b編碼

11.2.6 並行到串行轉換器(串行器)

11.2.7 差動發送驅動器

11.2.8 發送器(tx)時鐘

11.2.9 發送邏輯的其他主題

11.3 接收邏輯的細節

11.3.1 差動接收器

11.3.2 接收時鐘的恢復

11.3.3 串行到並行轉換器(反串行器)

11.3.4 符號邊界測定(符號鎖定)

11.3.5 接收器時鐘補償邏輯

11.3.6 通道到通道的相位補償

11.3.7 8b/10b解碼器

11.3.8 去擾頻器

11.3.9 字節反拆分

11.3.10 過濾器和數據包校正檢查

11.3.11 接收緩沖區(rx緩沖區)

11.4 物理層錯誤處理

第12章 電氣物理層

12.1 電氣物理層概述

12.2 高速電氣信令

12.2.1 時鐘要求

12.2.2 阻抗和終結

12.2.3 13(3共模電壓

12.2.4 esd和短路要求

12.2.5 接收器檢測

12.2.6 差動驅動器和接收器

12.2.7 電氣空閒

12.2.8 鏈路上發送線路的損耗

12.2.9 ac耦合

12.2.10 去矯(或預矯)

12.2.11 信標信令

12.3 lvds眼圖

12.3.1 抖動、噪音和信號衰減

12.3.2 眼測試(eye test)

12.3.3 最優眼

12.3.4 抖動可使眼邊加寬或變窄

12.3.5 噪音和信號衰減使眼變高

12.4 發送器驅動器特性

12.4.1 概述

12.4.2 發送驅動器一致性測試和測量負載

12.5 輸入接收器的特性

12.6 在各種電源狀態中的電氣物理層狀態

第13章 系統復位

13.1 兩類系統復位

13.1.1 基本復位

13.1.2 帶內復位或hot復位

13.2 退出復位

13.3 從l2低功率狀態中的鏈路喚醒

第14章 鏈路初始化和定向

14.1 鏈路初始化和定向概述

14.1.1 概述

14.2 鏈路定向和初始化期間所用的有序集

14.2.1 ts1和ts2有序集

14.2.2 電氣空閒有序集

14.2.3 fts有序集

14.2.4 skip有序集

14.3 鏈路定向和狀況狀態機(ltssm)

14.3.1 概述

14.3.2 ltssm各狀態概述

14.4 ltssm各狀態詳述

14.4.1 檢測狀態

14.4.2 輪詢狀態

14.4.3 配置狀態

14.4.4 恢復狀態

14.4.5 lo狀態

14.4.6 los狀態

14.4.7 l1狀態

14.4.8 l2狀態

14.4.9 hot復位狀態

14.4.10 禁用狀態

14.4.11 回環狀態

14.5 與ltssm相關的配置寄存器

14.5.1 鏈路功能寄存器

14.5.2 鏈路狀況寄存器

14.5.3 鏈路控制寄存器

第四部分 與電源有關的主題

第15章 功率預算

15.1 功率預算簡介

15.2 功率預算的各個要素

15.3 插槽功率極限控制

15.3.1 擴充端口的插槽功率極限

15.3.2 擴充設備限制功率消耗

15.4 功率預算功能寄存器組

第16章 電源管理

16.1 簡介

16.2 配置軟件的入門知識

16.2.1 pci pm基礎

16.2.2 onnow design initiative計劃定義了全部pm

16.2.3 pci express電源管理與acpi

16.3 設備功能的電源管理

16.3.1 pm功能寄存器組

16.3.2 設備的pm狀態

16.3.3 pci-pm寄存器詳述

16.4 鏈路電源管理簡介

16.5 鏈路活動狀態電源管理

16.5.1 los狀態

16.5.2 l1 aspm狀態

16.5.3 aspm退出延遲

16.6 軟件發起的鏈路電源管理

16.6.1 d1/d2/d3hot和l1狀態

16.6.2 l2/l3准備就緒——切斷鏈路的電源

16.7 鏈路喚醒協議和pme的生成

16.7.1 pme消息

16.7.2 pme序列

16.7.3 避免pme消息產生背壓(back pressure)死鎖

16.7.4 pme環境

16.7.5 喚醒無法通信的鏈路

16.7.6 輔助電源

第五部分 可選功能

第17章 熱插拔

17.1 背景

17.2 pci express環境下的熱插拔

17.2.1 突然移除通知

17.2.2 pci熱插拔和pci express熱插拔的區別

17.3 支持熱插拔所需的基本要素

17.3.1 軟件基本要素

17.3.2 硬件基本要素

17.4 卡移除與插人過程

17.4.1開與關狀態

17.4.2卡移除過程

17.4.3卡插入過程

17.5 標准使用模型

17.5.1 背景

17.5.2 標准用戶接口

17.6 標准熱插拔控制器信令接口

17.7 熱插拔控制器編程接口

17.7.1 插槽功能

17.7.2 插槽控制

17.7.3 插槽狀況和事件管理

17.7.4 卡插槽與服務器10模塊實現

17.8 插槽編號

17.8.1 物理插槽id

17.9 終止卡與驅動程序的活動

17.9.1 概述

17.9.2 驅動程序暫停(可選)

17.10 原語

第18章 附加卡與連接器

18.1 簡介

18.1.1 附加卡連接器

18.1.2 輔助信號

18.1.3 電氣要求

18.1.4 附加卡的互操作性

18.2 正在開發的外形規格

18.2.1 概述

18.2.2 服務器10模塊(siom)

18.2.3 提升卡

18.2.4 微型pci express卡

18.2.5 newcard外形規格

第六部分 pci express配置

第19章 配置概述

19.1 設備與功能的定義

19.2 主總線與二級總線的定義

19.3 系統啟動時拓撲未知

19.4 每種功能實現一組配置寄存器

19.4.1 簡介

19.4.2 功能配置空間

19.5 主機/pci橋的配置寄存器

19.6 由處理器發起的配置事務

19.6.1 僅根聯合體能發起配置事務

19.6.2 配置事務僅能向下游移動

19.6.3 沒有對等配置事務

19.7 配置事務通過總線、設備和功能號路由

19.8 如何發現功能

19.9 如何區分pci到pci橋與非橋功能

第20章 配置機制

20.1 簡介

20.2 pci兼容配置機制

20.2.1 背景

20.2.2 pci兼容配置機制說明

20.3 pci express增強配置機制

20.3.1 說明

20.3.2 規則

20.4 類型0配置請求

20.5 類型1配置請求

20.6 pci兼容配置訪問示例

20.7 增強配置訪問示例

20.8 初始配置訪問

20.8.1 初始化期間會發生什麼

20.8.2 pci中初始化階段的定義

20.8.3 pci-x中初始化階段的定義

20.8.4 pci express與初始化時間

20.8.5 運行期間對crs接收的rc響應

第21章 pci express枚舉

21.1 簡介

21.2 帶單個根聯合體系統的枚舉

21.3 枚舉帶多個根聯合體的系統

21.3.1 pci兼容配置機制的運行特征

21.3.2 增強配置機制的運行特征

21.3.3 枚舉過程

21.4 根聯合體或交換器內的多功能設備

21.4.1 根聯合體內的多功能設備

21.4.2 交換器內的多功能設備

21.5 嵌入交換器或根聯合體中的端點

21.6 記住你的身份

21.6.1 概述

21.6.2 根聯合體總線號/設備號的分配

21.6.3 在id分配前發起請求

21.6.4 在id分配前發起完成

21.7 根聯合體寄存器塊(rcrb)

21.7.1 rcrb地址中的問題

21.7.2 有關rcrb的其他信息

21.8 其他規則

21.8.1 分割配置事務要求單個完成

21.8.2 pci express到pci橋或pci express到pci-x橋的問題

21.8.3 pci特殊周期事務

第22章 pci兼容配置寄存器

22.1 頭類型0(header type 0)

22.1.1 概述

22.1.2 兼容pci的頭類型o寄存器

22.1.3 與pci不兼容的頭類型o寄存器

22.1.4 用於識別設備驅動程序的寄存器

22.1.5 頭類型寄存器

22.1.6 bist寄存器

22.1.7 功能指針寄存器

22.1.8 cardbus cis指針寄存器

22.1.9 擴展rom基址寄存器

22.1.10 命令寄存器

22.1.11 狀況寄存器

22.1.12 緩存行大小寄存器

22.1.13 主控器延時定時器寄存器

22.1.14 中斷線寄存器

22.1.15 中斷引腳寄存器

22.1.16 基址寄存器

22.1.17 min_gnt/max_lat寄存器

22.2 頭類型1(header type 1)

22.2.1 概述

22.2.2 兼容pci的頭類型1奇存器

22.2.3 與pci不兼容的頭類型1寄存器

22.2.4 術語

22.2.5 總線號寄存器

22.2.6 廠商id寄存器

22.2.7 設備id寄存器

22.2.8 修訂版id寄存器

22.2.9 類代碼寄存器

22.2.10 頭類型寄存器

22.2.11 bist寄存器

22.2.12 功能指針寄存器

22.2.13 基本事務過濾機制

22.2.14 橋的存儲器、寄存器組和設備rom

22.2.15 橋的io過濾器

22.2.16 橋的可預取存儲器過濾器

22.2.17 橋的存儲器映射io過濾器

22.2.18 橋命令寄存器

22.2.19 橋狀況寄存器

22.2.20 橋高速緩存行大小寄存器

22.2.21 橋延遲定時器寄存器

22.2.22 與橋中斷有關的寄存器

22.3 pci兼容功能

22.3.1 agp功能

22.3.2 關鍵產品數據(vpd)功能

22.3.3 機箱/插槽編號寄存器簡介

22.3.4 機箱與插槽號的分配

第23章 擴展rom

23.1 rom的作用——可在啟動期間使用的設備

23.2 rom檢測

23.3 必需的rom映射

23.4 rom的內容

23.4.1多代碼映像

23.4.2 代碼映像的格式

23.5 初始化代碼的執行

23.6 開放固件簡介

23.6.1 概述

23.6.2 通用設備驅動程序的格式

23.6.3 傳遞資源列表到即插即用os

第24章 express專用配置寄存器

24.1 簡介

24.2 pci express功能寄存器組

24.2.1 簡介

24.2.2 必需的寄存器

24.2.3 插槽寄存器

24.2.4 根端口寄存器

24.3 pci express擴展功能

24.3.1 概述

24.3.2 高級錯誤報告功能

24.3.3 虛擬信道(vc)功能

24.3.4 設備序列號功能寄存器組

24.3.5 功率預算功能寄存器組

24.4 rcrb

24.4.1 概述

24.4.2 固件向os提供每個rcrb的基地址

24.4.3 對rcrb的不對齊或鎖定訪問

24.4.4 rcrb中的擴展功能寄存器組

24.4.5 rcrb丟失鏈路

附錄a 測試、調試和驗證

a.1 目的

a.2 串行總線的拓撲結構

a.3 雙單工

a.4 設置分析儀、捕獲和觸發條件

a.5 鏈路定向,通信的第一步

a.6 插槽連接器與mid-bus墊

a.7 練習:深入的驗證

a.8 信號完整性、設計和測量

a.8.1 概述

a.8.2 高速pcb的設計要求

附錄b pci express體系結構的市場及應用

b.1 簡介

b.2 企業計算系統

b.2.1 桌面系統

b.2.2 服務器系統

b.2.3 嵌入式控制系統

b.2.4 存儲系統

b.2.5 通信系統

b.3 小結

附錄c 用pci express技術實現智能適配器和多主機系統

c.1 簡介

c.2 使用模型

c.2.1 智能適配器

c.2.2 主機故障轉移

c.2.3 多處理器系統

c.3 使用pci的多處理器實現歷史

c.4 在pci express基本系統中實現多主機/智能適配器

c.4.1 示例:在pci express基本系統中實現智能適配器

c.4.2 示例:在pci express系統中實現故障轉移

c.4.3 示例:在pci express基本系統中實現雙主機

c.5 小結

c.6 地址轉換

c.6.1 直接地址轉換

c.6.2 基於查找表的地址轉換

c.6.3 下游bar限界寄存器

c.6.4 轉發64位地址的存儲器事務

附錄d 類代碼

附錄e 鎖定事務系列

e.1 簡介

e.2 背景

e.3 pci express鎖定協議

e.3.1 鎖定消息——虛擬鎖定信號

e.3.2 鎖定協議序列——一個示例

e.4 鎖定規則小結

e.4.1 與鎖定事務的發起和傳播有關的規則

e.4.2 與交換器有關的規則

e.4.3 與pci express/pci橋有關的規則

e.4.4 與根聯合體有關的規則

e.4.5 與傳統端點有關的規則

e.4.6 與pci express端點有關的規則

- 上一頁:《Windows網絡與通信程序設計》掃描版[PDF]

- 下一頁:《JavaScript DOM高級程序設計》(AdvancED DOM Scripting Dynamic Web Design Techniques)掃描版[PDF]

相關資源:

- [人文社科]《超級全景霸王兵器Ⅱ:超級戰車》掃描版[PDF

- [人文社科]《托福寫作》(Perfect Phrases for the TOEFL Speaking and Writing Sections)英文版[PDF]

- [計算機與網絡]《嵌入式C編程與Atmel AVR》(Embedded C Programming and the Atmel AVR)第2版[PDF]

- [生活圖書]《YOU:身體使用手冊》掃描版[PDF]

- [文學圖書]《筆記大自然》掃描版[PDF]

- [小說圖書]《不能沒有她》掃描版[PDF]

- [少兒圖書]《小學語文拼音偏旁卡音頻》

- [其他圖書]《傳統八卦掌第二冊》掃描版[PDF]

- [小說圖書]《布拉熱洛納子爵》(The Vicomte of Bragelonne)英文文字版[PDF]

- [其他圖書]《蛻變-從菜鳥到Linux安全專家》掃描版[PDF]

- [人文社科]《逃亡鳄魚島》(Rogue)配音版

- [電腦基礎]《高質量鳥瞰商業素材》(DOSCH : Birds Eye - Trees)[ISO]

- [人文社科]夏韶聲 -《谙Ⅲ》[APE]

- [學習材料]《人體素描技法》(人體のデッサン技法)再版[PDF] 資料下載

- [學習材料]《在宋美齡身邊的日子(第2版)》資料下載

- [文學圖書]《有一種病叫愛情》掃描版[PDF]

- [應用軟件]《Ashampoo 辦公套件 2008》(Ashampoo Office 2008 v3.0 Multilingual)多國語言版含簡體中文

- [人文社科]《女權主義》清晰掃描版[PDF]

- [經濟管理]《管人管事有絕招》掃描版[PDF]

- [行業軟件]《DELCAM ArtCAM Insignia V4.019雕刻設計》(DELCAM ARTCAM INSIGNIA V4.019

- 《傻瓜操作系統系列》(Operation System for Dummies)文

- 《現代體系結構的優化編譯器》(Optimizing Compilers for Modern Architectures,A Dependence-Based Approach )((美)Randy Allen,Ken Kennedy)掃描版[PDF]

- 《 黑客反匯編揭秘:第二版(附屬程序+PDF完整版)》(Hacker Disassembling Uncovered)PDF+附屬程序完整版

- 《開發自己的搜索引擎:Lucene+Heritrix》第2版[PDF]

- 《軟件測試與持續質量改進(第3版)》(Software Testing and Continuous Quality Improvement, Third Edition)掃描版[PDF]

- 《魔獸爭霸—上古之戰三部曲》(Warcraft—War of

- 《Photoshop CS5數碼生活照片的修飾與個性化處理》掃描版[PDF]

- 《Unix-linux編程實踐教程 中文清晰》(Understanding

- 《網絡密碼-中國第一代黑客攻伐實錄》掃描版[PDF]

- 《Java加密與解密的藝術》(Java加密與解密的藝術

- 《日賺500元2:互聯網創業實操指南》掃描版[PDF]

- 《Pro/ENGINEER野火版3.0機構仿真運動實例精講》掃

免責聲明:本網站內容收集於互聯網,本站不承擔任何由於內容的合法性及健康性所引起的爭議和法律責任。如果侵犯了你的權益,請通知我們,我們會及時刪除相關內容,謝謝合作! 聯系信箱:[email protected]

Copyright © 電驢下載基地 All Rights Reserved