電驢下載基地 >> 软件资源 >> 編程開發 >> 《開源可擴充處理器架構 源代碼 》(OpenSPARC Source code)2009 UP [VIS多媒體指令集][壓縮包],編程開發、資源下載

| 《開源可擴充處理器架構 源代碼 》(OpenSPARC Source code)2009 UP [VIS多媒體指令集][壓縮包],編程開發、資源下載 | |

|---|---|

| 下載分級 | 软件资源 |

| 資源類別 | 編程開發 |

| 發布時間 | 2017/7/13 |

| 大 小 | - |

《開源可擴充處理器架構 源代碼 》(OpenSPARC Source code)2009 UP [VIS多媒體指令集][壓縮包],編程開發、資源下載 簡介: 中文名: 開源可擴充處理器架構 源代碼 英文名: OpenSPARC Source code別名: OpenSPARC 源代碼 資源格式: 壓縮包版本: 2009 UP [VIS多媒體指令集]發行時間: 2009年制作發行: www.opensparc.net地區: 美國語言: 英文簡介: 引用XDR 內存開發資料更新自述 XDR(eXtremeDataRate)內存是Rambus開

電驢資源下載/磁力鏈接資源下載:

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].OpenSPARC.T1.Source.code.v1.7.iso

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].OpenSPARC.T2.Source.code.v1.3.iso

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].Simply.RISC.S1.Source.code.7z

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].Leon3.Source.code.7z

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].OpenSPARC.Internals.Book.pdf

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].Sun.CMT.MultiThread.WP.pdf

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].OpenSPARC.Documents.7z

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].HyperTransport.IP.Core.7z

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].XDR.DRAM.Development.Documentation.7z

- 下載位址: [www.ed2k.online][開源可擴充處理器架構.源代碼.].VIS.Instruction.Set.7z

- 下載位址: [www.ed2k.online]SRISC-S1-M1.tar.gz

全選

"《開源可擴充處理器架構 源代碼 》(OpenSPARC Source code)2009 UP [VIS多媒體指令集][壓縮包],編程開發、資源下載"介紹

中文名: 開源可擴充處理器架構 源代碼 英文名: OpenSPARC Source code別名: OpenSPARC 源代碼 資源格式: 壓縮包版本: 2009 UP [VIS多媒體指令集]發行時間: 2009年制作發行: www.opensparc.net地區: 美國語言: 英文簡介:

引用XDR 內存開發資料更新自述

XDR(eXtremeDataRate)內存是Rambus開發的一種高帶寬傳輸內存技術。SPARC處理器若加入此技術更能提供產品性能與競爭力。

引用HyperTransport Bus 更新自述

鑒於AMB、J-Bus、PCIE總線功能有限,特補上HyperTransport Bus以供參考。希望對你有用。

引用OpenSPARC T2 1.3 更新概述

A fully synthesizable, reduced footprint, System-level model has been developed, suitable for FPGA and Emulation Platforms. This model has single OpenSPARC T2 core, crossbar interconnect, and WISHBONE Memory Controller ( from www.opencores.org). This environment supports RTL Simulation, FPGA Synthesis and Gate-level simulation with a one-to-one correspondence (i.e a given test runs unchanged in the RTL Gate environments.) This environment is hardware platform neutral and can be ported on any FPGA prototyping board.

Specifically, following new flows are supported with this release:

* Added design compile-time flag 'FPGA'. Inclusion of this flag at the simulation or compile time will make design synthesizable with the FPGA tools. We have primarily tested this with Synplicity tool chain

* Added new regression environment in sims which allows full-system (core, crossbar, wishbone, memory controller) to be simulated in software.

* FPGA synthesis script 'fpga_synth' is provided to automate the synthesis of the design on FPGAs. Script is general enough to be used with any FPGA device or any vendor synthesis tool

* Finally, FPGA netlist simulation environment is provided to verify the functionality of the FPGA netlist

OpenSPARC 源代碼

[已通過安全檢測]RISING.ANTIVIRUS.Personal.Edition.2008.Retail

[病毒庫發布日期]2008-11-04

[已通過安裝測試]Windows XP Professional + Service Pack 3

共享服務時間:通常隨機

共享服務器:通常Razorback 3.1/Razorback 3.0

軟件版權歸原作者及原軟件公司所有 請遵循GPL授權協議使用

SPARC

Sun UltraSPARC II處理器

SPARC,全稱為“可擴充處理器架構”(Scalable Processor ARChitecture),是RISC微處理器架構之一。它最早於1985年由升陽電腦所設計,也是SPARC國際公司的注冊商標之一。這家公司於 1989年成立,其目的是向外界推廣SPARC,以及為該架構進行符合性測試。此外該公司為了擴闊SPARC設計的生態系統,SPARC國際也把標准開放,並授權予多間生產商采用,包括德州儀器、Cypress半導體、富士通等。由於SPARC架構也對外完全開放,因此也出現了完全開放原始碼的LEON 處理器,這款處理器以VHDL語言寫成,並采用LGPL授權。

SPARC架構原設計給工作站使用,及後應用在升陽、富士通等制造的大型SMP服務器上。而升陽開發的Solaris操作系統也是為SPARC設計的系統之一,除Solaris外,NeXTSTEP、Linux、FreeBSD、OpenBSD及NetBSD系統也提供SPARC版本。

現時最新版本的SPARC為第8及第9版,在2005年12月,升陽方面宣布其UltraSPARC T1處理器將采用開放原始碼方式。

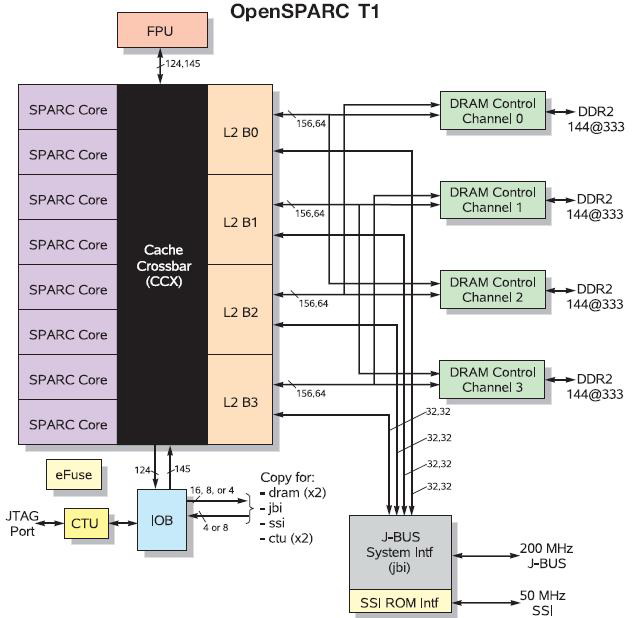

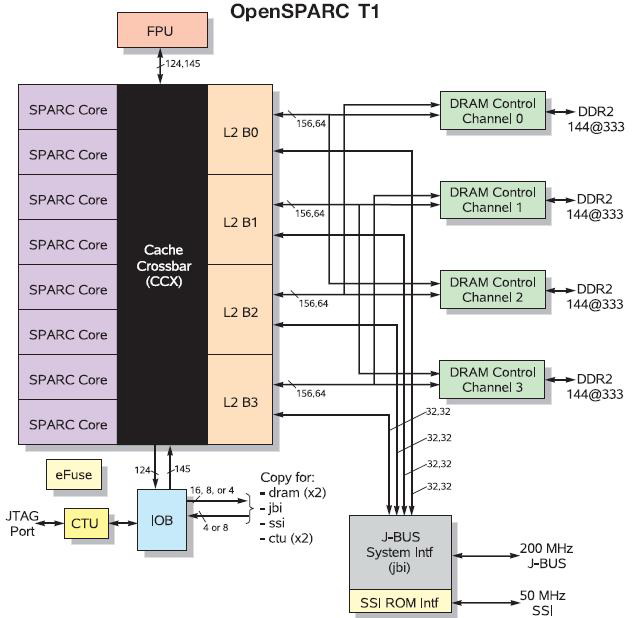

開源CPU--OpenSparc T1簡介 FPGA級別

2006年3月,Sun宣布開源化其多核心UltraSparc T1 CPU的處理器設計,采用的是GNU通用公共許可證(GNU GPL license)。之前Sun已經公開了 Hypervisor API規范,允許各公司將Linux、BSD 及其他操作系統移植到UltraSparc T1平台。

Sun是業界首家將復雜的硬件設計使用GNU GPL許可進行發布的公司,而此舉也將為UltraSparc T1處理器增加曝光度,並吸引開發人員為該平台開發軟硬件解決方案。

該硬件設計的開源發布包括64-bit UltraSparc T1的Verilog硬件描述語言源代碼,驗證套裝和模擬模型,ISA規范及Solaris 10 OS虛擬鏡像。T1處理器的代號為“Niagara”,於去年發布並應用於Sun的T1000/T2000服務器中。 Sun目前推出了4、6、8核心的CPU版本,且每核心最多支持4線程,即總共最多32線程。T1基於Sparc V9架構,每核心集成16KB指令緩存和8KB主數據緩存,整個處理器共享3MB L2緩存。“OpenSparc T1”芯片設計,驗證套裝,架構和性能模型工具已經發布在http://www.opensparc.net網站。Sun還發布了“Cool Tools”,其中包括優化多線程CPU性能的各種程序以及CMT編程及描繪工具。

OpenSparc T1處理器的主要特征包括:

8個Sparc V9處理核心,每核心4線程,共計32線程

每處理核心16KB一級指令緩存,共128KB;

每處理核心8KB一級數據緩存,共64KB;

3MB二級緩存,4-way bank,12向關聯,各核心共享;

4個DDR2內存控制器,每通道位寬144bit,總帶寬峰值25GB/s;

IEEE754兼容浮點單元(FPU),各核心共享;

J-Bus輸入輸出接口,峰值帶寬2.56GB/s,128bit多元地址/數據復用總線。

UltraSPARC T1

Sun UltraSPARC T2解析

新一代的UltraSPARC T2處理器帶有8個核心,可以同時處理64個線程。T2的產品代號Niagra 2,不僅將應用在SUN自己的服務器上,還可能放在機頂盒、路由器等設備中。目前處理器由TI負責制造,采用SoC設計,帶有2個以太網接口,1個 PCIe ×8接口和4個雙通道FBDIMM內存控制器,整個處理器帶有5.03億個晶體管,核心大小342平方毫米,目前共推出1.2GHz與1.4GHz兩種頻率,在1.4GHz主頻的電壓為1.1伏,工作頻率上功耗85W。

UltraSPARC T2設計藍圖

65納米技術更節能

SUN已經成功將90納米的制作工藝成功轉制成65納米工藝,這樣意味著在同樣面積的芯片上可以放入更多的模塊。此外,T2還使用了其具有革命性的酷線程(CoolThreads?)芯片多線程技術(CMT)擴展到每線程功耗低於2瓦的UltraSPARC T2處理器。換句話說,擁有這項技術後,SUN的產品功耗將是競爭對手的十分之一或三十分之一。因此我們將看到業界功耗最低、8個內核、64個線程、4倍的吞吐量及網絡和安全的功能性於一身的產品。

芯片特點

處理器 八核心 工作主頻在900MHz – 1.4GHz

支持64線程

支持64 FB-DIMMs, 4個內存控制器

內存帶寬 60+GB/S

功耗 標准95W或最高123W

其他特點 8個浮點運算單元(FPUs)

雙10Gbit以太網接口和PCI-E支持

4MB二級緩存 (8 banks)

每核心1個安全協處理器

核心特點

核心特征 大小:12 mm2

8線程

2條指令管線 + 1個浮點計算 + 1個密碼加速單元

8KB 數據緩存+ 16KB 指令緩存

其他應用

其他應用 單插槽的機架或刀片服務器

WiMAX 無線

3G/4G

網絡基礎構架

性能翻倍,新一代架構有突破

UltraSPARC T2處理器將單一芯片上集成的系統功能提升到空前水平,在性能方面也是T1的兩倍。這首先要得益於它較高的吞吐量處理器能力,在 SPECint_rate2006和SPECfp_rate2006的測試中,這兩項成績分別是78.3 est和62.3 est,這主要得益於該處理器的8核和每核8線程的設計特色。在網絡連接方面,該處理器支持兩個可虛擬化的多線程的每秒10千兆比特的以太網端口,也就是萬兆以太網接口,並具有內建的包分類功能。在安全方面,8個密碼加速單元,一共有10個獨立的功能,可滿足不斷增長的安全需求,包括由NSA批准的算法,在性能上也沒有任何損失。

除此之外,在計算方面8個浮點單元,SUN將CMT的技術優勢擴展到了高性能計算領域,適用於各類科學應用,創立了單芯片 SPECfp_rate2006世界記錄和單芯片,有8條通道的輸入輸出接口可以滿足行業標准PCI Express I/O高速應用,如流媒體、數據庫讀/寫,以及數據備份等。4個內存控制器,提供了每秒50千兆字節以上的內存訪存速度。

以下表格中公布的是UltraSPARC T2單處理器的性能測試結果:

SPECint_rate2006 SPECfp_rate2006

1.4GHz Sun UltraSPARC T2 148% 134%

4.7GHz IBM POWER 6 115% 125%

2.66GHz Intel X5355 100% 100%

開源讓更多用戶受益

UltraSparc T2也將和UltraSparc T1一樣采用開放原始碼授權,到目前為止,OpenSPARC T1源碼的下載已經超過5,500次。現在Sun正准備將UltraSPARC T2的源碼在www.opensparc.net上向OpenSPARC社團發布。並且提供了程序員參考手冊、微架構技術規范、OpenSPARC T2β版評估項目等一系列措施,其中程序員參考手冊裡提供了軟件端口、操作系統端口,以及加快OpenSPARC T2項目進展的應用工具。微架構技術規范裡提供了對OpenSPARC T2硬件模塊特性和功能的詳細描述。OpenSPARC T2β版評估項目為一定數量的硬件設計人員和工具開發人員提供早期試用版,讓他們開始使用具有片上系統功能性的最新CMT技術。該項目將促進 OpenSPARC T2社團的發展,加快調試過程,以獲得性能更佳的OpenSPARC T2的第一個版本,配合具有海量線程特性的Solaris操作系統使高線程處理器UltraSPARC T2的技術優勢得到充分發揮,擁有開放的、低成本的虛擬化功能。

OpenSPARC Internals

This book is intended as a getting started companion to both OpenSPARC T1 and OpenSPARC T2. Now that Sun has open-sourced OpenSPARC T1 and T2, what can they be used for? One thing is certain: the real-world uses to which OpenSPARC will be put will be infinitely more diverse and interesting than anything that could be suggested in this book! OpenSPARC Internals was largely written by the team of OpenSPARC designers, developers, and programmers to acquaint readers with OpenSPARC and to guide users as they develop their own OpenSPARC designs. Here are some highlights of the book:

How to customize and use OpenSPARC

How to start using OpenSPARC code

How to make basic changes including

configuring number of cores or threads

paring to a smaller size

fitting on an FPGA

adding extensions

How to set up

simulation environment

emulation environment

How to verify an OpenSPARC design

OpenSPARC Internals

Edited by David Weaver

Published by Sun Microsytems, Inc.

369 pages

First printing, October 2008

ISBN 978-0-557-01974-8

What are they saying about OpenSPARC Internals?

The coverage is extremely broad and deep, from the basics of the OpenSPARC architecture, the rationale for throughput optimized microprocessor design, and the microarchitecture of the T1 and T2 implementations to a roadmap for using the T1 and T2 design database and design verification suites.

Kunle Olukotun

Stanford University

Professor, Electrical Engineering Computer Science

Founder, Afara Websystems

Director, Pervasive Parallelism Lab

OpenSPARC Internals provides an in-depth explanation of UltraSPARC T1/T2 internal architecture. It also serves as a detailed reference for guiding the implementation of a chip multithreaded microprocessor or the development of a SoC based application system. This book plays a significant role in helping promote not only the application of UltraSPARC T1/T2 but also the research and development of a chip multithreaded microprocessor as well as its applications.

Dongsheng Wang, Ph.D.

Tsinghua University, Beijing, China

Professor, Dept. of Computer Science

Director of Microprocessor and SoC Center

Like the open-source OpenSPARC T1 and T2 projects, OpenSPARC Internals delivers a comprehensive package. The book tells a complete story behind Sun's current flagship chip-multithreaded (CMT) processors-from the design theories and internals to the development tools and methodologies. The book is especially indispensable to anyone interested in uncovering ways to take advantage of the open-source OpenSPARC projects.

James C. Hoe

Carnegie Mellon University

Associate Professor, Electrical Computer Engineering

This book provides a wealth of practical tips for getting started using OpenSPARC, and OpenSPARC provides a great design to take full advantage of modern FPGAs.

Ivo Bolsens Chief Technology Officer, Xilinx Corporation

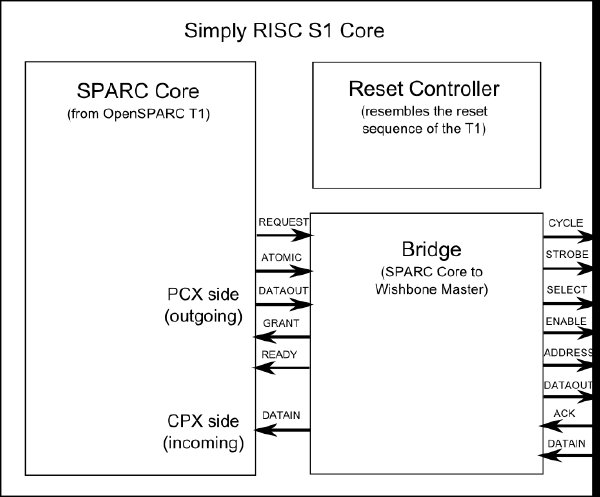

引用Simply RISC S1 Core

Written by Administrator

Monday 10 November 2008

Simply RISC S1 Core is a cutdown version of the OpenSPARC processor released as open-source by Sun Microsystems. The current version is based on the latest OpenSPARC T1 v1.6.

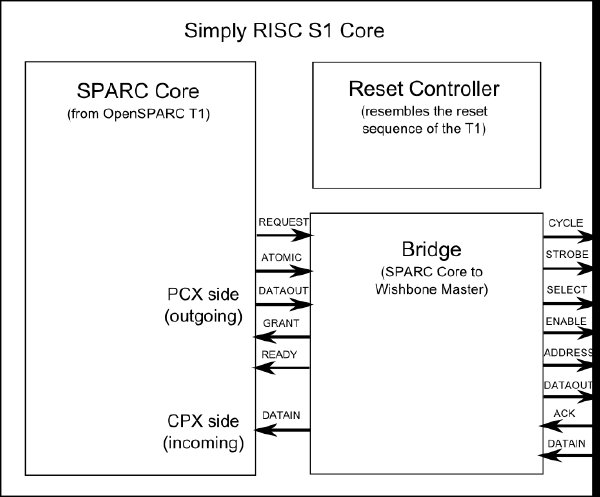

While OpenSPARC T1 (codename Niagara) features 8 SPARC CPU Cores and several peripherals, Simply RISC S1 Core (codename Sirocco) takes only one 64-bit SPARC Core from that design and adds a Wishbone/AMBA bridge and a simple reset controller:

Simply RISC S1

The whole process of designing a Wishbone bridge for the SPARC Core has been detailed in Chapter 11 of the book OpenSPARC Internals; the design now also supports an AMBA bridge as explained on the home page.

The enviroment contains scripts that support the use of three different flavors of the S1 Core; the following table summarizes the synthesis results obtained with Xilinx tools:S1 Core version Description Virtex-5 Area (*)

S1 Core EE Four threads, usual 16K+8K L1 caches 60K LUTs

S1 Core SE One thread, usual 16K+8K L1 caches 40K LUTs

S1 Core ME One thread, no L1 caches 37K LUTs

(*) Number of Slice LUTs on Virtex-5 devices, pre-Place-and-Route, obtained with provided push-button script

引用HyperTransport

HyperTransport技術是一種高速、低延時、點對點的連接,旨在提高電腦、服務器、嵌入式系統,以及網絡和電信設備的集成電路之間的通信速度。它的速度比某些現有技術高出48倍。

HyperTransport有助於減少系統之中的布線數量,從而能夠減少系統瓶頸,讓當前速度更快的微處理器能夠更加有效地在高端多處理器系統中使用系統內存。

HyperTransport技術的設計目的是:

提供比現有技術高得多的帶寬

使用低延時響應和較少的引腳數

在保持與傳統電腦總線的兼容性的同時,可以擴展到新的SNA(系統網絡架構)總線

對操作系統保持透明,對周邊設備驅動程序的影響極小

HyperTransport技術由AMD和眾多行業合作伙伴共同開發而成,由 HyperTransport技術聯盟(一家位於得克薩斯的非盈利性企業)管理和發放許可。如需查看關於HyperTransport的全部規格和更多信息,請訪問HyperTransport.org。

HyperTransport雙向傳輸總線技術,相對於過去的PCI總線設計而言,Hyper Transport技術從根本上有了顯著的提高。從單純的數據比較來看,Hyper Transport在數據傳輸率上達到了驚人的12.8GB/s,這個數值相比Intel最新3GIO技術的最初理論傳輸率高出了很多(3GIO早期產品的帶寬設計為2.5GB/s,遠景規劃為10GB/s)。同目前的PCI總線而言,HyperTransport的數據傳輸率高出了整整96倍以上

HyperTransport最初是AMD在1999年提出的一種總線技術,隨著AMD64位平台的發布和推廣,HyperTransport應用越來越廣泛,也越來越被人們所熟知。

HyperTransport是一種為主板上的集成電路互連而設計的端到端總線技術,它可以在內存控制器、磁盤控制器以及PCI總線控制器之間提供更高的數據傳輸帶寬。HyperTransport采用類似DDR的工作方式,在400MHz工作頻率下,相當於800MHz的傳輸頻率。此外HyperTransport是在同一個總線中模擬出兩個獨立數據鏈進行點對點數據雙向傳輸,因此理論上最大傳輸速率可以視為翻倍,具有4、8、16及32位頻寬的高速序列連接功能。在400MHz下,雙向4bit模式的總線帶寬為0.8GB/sec,雙向 8bit模式的總線帶寬為1.6GB/sec;800MHz下,雙向8bit模式的總線帶寬為3.2GB/sec,雙向16bit模式的總線帶寬為 6.4GB/sec,雙向32bit模式的總線帶寬為12.8GB/sec。以400MHz下,雙向4bit模式為例,帶寬計算方法為 400MHz×2×2×4bit÷8=0.8GB/sec。

HyperTransport還有一大特色,就是當數據位寬並非32bit時,可以分批傳輸數據來達到與32bit相同的效果。例如16bit的數據就可以分兩批傳輸,8bit的數據就可以分四批傳輸,這種數據分包傳輸的方法,給了 HyperTransport在應用上更大的彈性空間。

2004年2月,HyperTransport技術聯盟(Hyper Transport Technology Consortium)又正式發布了HyperTransport 2.0規格,由於采用了Dual-data技術,使頻率成功提升到了1.0GHz、1.2GHz和1.4GHz,數據傳輸帶寬由每通道1.6Gb/sec 提升到了2.0GB/sec、2.4Gb/sec和2.8GB/sec,最大帶寬由原來的12.8Gb/sec提升到了22.4GB/sec。

當HyperTransport應用於內存控制器時,其實也就類似於傳統的前端總線(FSB,Front Side Bus),因此對於將HyperTransport技術用於內存控制器的CPU來說,其HyperTransport的頻率也就相當於前端總線的頻率。

******************************************

為什麼才會誕生HyperTransport

Intel從82810芯片組開始,創造了自己的Hub Link技術來連接南北橋芯片,使得當時810芯片組成為最能發揮Ultra DMA66傳輸性能的芯片組。因為Intel的授權費用高昂,所以很多的台灣芯片組廠商為了不向Intel取得Hub Link (8bit,133Mhz,266MB/Sec)技術授權。為了彌補在性能上可能產生的劣勢,芯片組廠商都開發自己的技術來解決這一問題。例如VIA開發了V-Link(32bit,66Mhz,266MB/Sec),SIS也開發了他們自己的DPI(Dedicated Pci to Ide bus,266MB/Sec)或者是最新的Multi-threaded IO Link(1.2GB/Sec)。

AMD也同樣針對自己的CPU設計有支持的芯片組,他們同樣必須面對如何連接南北橋才能更好的發揮Ultra DMA 66/100的效能問題。AMD的技術絕對可以達到這個水平,但是AMD的目的是不想開發獨自一家的芯片組技術,而是想制訂出一種能適用於各種高速度芯片組之間的傳輸界面,這就是LDT (Lightning Data Transport),2001年2月改名為HyperTransport。

HyperTransport的發展之路

HyperTransport的前身稱為LDT,最早在99年的MicroProcessor Forum就提出了這個高速傳輸接口界面,當時是同 SiedgeHammer CPU一同提出的。不過當時的LDT技術幾乎就只能說純粹是個想法而已,一直到2000年5月份的時候,才正式推出了它的1.0版,有了運行規格,但當時沒有完成任何電氣規格方面的設計,只是到了目前才完善了電氣規格方面的制定(目前為1。01C版本,需要通過AMD的授權才能正式獲得。)

在2000 WinHEC上,AMD再次將LDT技術搬上講壇,據說當時有1500個廠商代表出席參加,整個會場爆滿。然後開始有了HyperTransport的技術白皮書。之後的2000年6月Platform 2000技術會議上AMD再次將LDT技術,擺上桌面。人們一次次接觸到這項新技術,越發感興趣,加上優秀的性能,很大程度上促進了 HyperTransport技術的發展。

HyperTransport技術概要

HyperTransport除了可以將芯片間數據的高速傳輸之外,它還具有 封包傳輸技術(Packet-Based) 、 雙條單向數據流及點對點的數據連接方式 、 彈性數據帶寬 等。使用HyperTransport自然是有它的道理的,它的可以改善系統數據傳輸的瓶頸,可以為系統設計人員制造更高效能的系統設備提供基礎,完完全全的加快整個系統性能運行效能,好處可以說是接踵而來。 HyperTransport到底有多快呢?峰值可以達到6.4GB/Sec,就拿現在的Hub Link、V-Link,DPI等技術來看,HyperTransport是他們的24倍,對於32bit、33.33Mhz的PCI相比,是PCI的 48倍。看到這裡我想你已經很明白我們為什麼要HyperTransport技術啦!

那些設備可能要用到HyperTransport技術

既然HyperTransport技術帶來性能的提升如此之高,那麼那些系統會需要高速數據交流和高速芯片組呢?

1、 網絡路由器

2、 網絡交換機

3、 網絡集線器

4、 服務器

5、 工作站

除了這些設備,本人覺得還不完善。在個人的設備和家庭設備上也完全可以使用。未來的手持通訊設備、家庭計算機網絡設備等,都是HyperTransport技術可以完全發揮作用的地方。

HyperTransport技術對於網絡傳輸方面的性能提高

現在的網絡設計簡直就是為了自身服務器能力的高效時代,所有的設備都需要高檔。就連Intel 方面的Pentium 4都自稱 NetBurst 運算構架,特別強調對於網絡方面有性能的提高。同樣在AMD方面也有HyperTransport的數據處理技術,也是同樣大力宣傳對網絡系統可以帶來非常之大的宣傳。因為現在的環境是這樣,只有這樣才能吸引人。HyperTransport對與網絡方面的幫助,主要在於電腦系統同網絡設備同時才用HyperTransport技術時,才可能得到非常高效的性能提高。其中包括WEB服務器使用的HyperTransport、寬帶網絡數據設備的HyperTransport、TCP-IP交換機使用的HyperTransport、防火牆使用的HyperTransport、工作站使用的HyperTransport、打印系統使用的HyperTransport、桌面電腦使用的HyperTransport等等。所有的硬件系統都用上HyperTransport的技術,自然而然網絡速度方面也會有一個飛越。

HyperTransport的技術合作伙伴

HyperTransport不僅僅對電腦效能方面有幫助,在網絡設備和通訊設備方面都有很高的性能提高。對於提出這一技術的AMD自身來說,至少有兩個地方可以使用到HyperTransport:

AMD的芯片組

在過去的年代裡南北橋芯片組以33bit、33MHz的PCI界面連接,但是隨著UDMA 66/100的傳輸技術出現後,不足以應付這些資料的傳輸速度。現在HyperTransport出現後,完全可以取代PCI,而且足以應付PCI-X、 66.66MHz PCI都游仞有余。

AMD的多處理器架構

從Athlon開始就可以支持多處理器運行的架構,但是AMD現在使用的EV6匯排流總線似乎難以應付大容量數據的處理,為了未來的K8或者更強大的處理器多顆並行使用的時候,如果使用HyperTransport接口來做數據資料的傳輸,你可以想象帶寬所帶來的性能提高。

其他更多的廠商

其實在其它系統上有100多家的廠商和AMD在共同研究、討論和推廣HyperTransport。其中有代表性的為一下幾家:

Cisco 路由器、交換機

Sun 服務器、工作站、

Via 處理器、芯片組、顯示芯片、其它芯片

Sis 芯片組、顯示芯片、其它芯片

Ali 芯片組、其它芯片

AMP 網絡連接器和接插件

Broadcom 寬帶網絡控制芯片

Phoenix BIOS、硬件底層程序

Fujitsu PC個人機、激光打印機、MO、硬盤

TYAN 主板、PC個人機

Nvidia 芯片組、顯示芯片、多媒體芯片

Ati 芯片組、顯示芯片、多媒體芯片

ALTERA 邏輯程控芯片

HyperTransport的運行規格

HyperTransport最吸引人的地方在那裡,就是在於那6.4GB的高速傳輸速度。 HyperTransport是由兩條點對點的單向數據傳輸路徑組成(一條為輸入、一條為輸出)。兩條單向傳輸路徑的數據帶寬是可以根據數據量的大小而彈性改變,最低的有2bit,可以調節為4bit、8bit、16bit、32bit,HyperTransport的運行在400MHZ的時鐘頻率下,但是使用的是DDR SDRAM相同的雙鐘頻觸發技術,所以在400MHZ的額定頻率下,其實是相當與工作在800MHZ的效能,正是如此每個數據的資料傳輸路徑最高可以有 800Mb/Sec。如果這樣來計算,當輸入輸出的資料輸出路徑都設置到最高的32bit時,然後以全速度400MHz DDR(相當於800MHZ)的時鐘頻率運行,這時數據最高的傳輸率就出現了---6.4GB/Sec。但是當傳輸的數據路徑的數據寬度降低為非 32bit,那麼傳輸數據的速度也自然下降。不過HyperTransport還有一大特色就是當數據資料寬度為非32bit (4byte)時,可以分批傳輸數據來達到32bit相同的效果,比如說16bit的數據就分兩批傳輸,在使用8bit數據時就分4批傳送,這種分包傳輸數據的方法,給了HyperTransport更大的彈性空間,最小4byte,最大64byte。對於資料快速傳輸帶來了很大的形式上的改良,提高了系統數據處理性能。

HyperTransport與其它系統接口界面速度比較

接口界面 峰值資料傳輸速度

PCI(32bit 33.33MHz) 132MB/Sec

PCI(64bit 66.66MHz) 528MB/Sec

PCI-X 1GB/Sec

InifiBand 4GB/Sec

HyperTransport 6.4GB/Sec

HyperTransport的電氣規格

HyperTransport采用的是所謂的差動式數據傳輸,這於Ultra SCSI/2 LVD或者USB數據傳輸方式是相同的,既每個bit都是用兩條傳輸線的電壓之間的差異來傳輸數字信號,當A線路的電壓電位高於B線路時,看做 1 ,反之為 0 。高速數據傳輸的特點通常是要使用非常之低的運行電壓,對於HyperTransport來說這點也是十分正確的。 HyperTransport的運行電壓為1.2V,電壓可以接受的差異標准是正負5%(差異600mV),換句話說來說就是在1.26-1.14V之間都是可以接受正確邏輯傳輸信號,這是針對信息發送方面的定義,在數據接收方面則為200mV的電壓差異。可見HyperTransport傳輸的偏差允許還是比較大的。同SCSI和IDE的規范相同,HyperTransport也需要在傳輸路徑中要有終端電阻,但是只要100歐姆的電阻即可,大大減低了電阻的成本。而且在采用HyperTransport的主板上,只要設計的線路不要超過24英寸,就能保證先前提到的800Mbit/Sec的數據傳輸率。

用HyperTransport取代PCI

AMD決定用HyperTransport用在自家的芯片組上來取代使用已久的PCI。既然如此應該有超越PCI的地方,對此AMD做了專門的解釋。下圖就是它的數據處理規格。(圖Hypertech4.bmp)我們都是知道 HyperTransport是每一個數據有是有2個資料線路來傳輸數據的,也就是說每bit就擁有2條傳輸資料的線路,上圖給出了各種信號的線路,大家自己相加一下就知道可以使用多少線路。當8bit的HyperTransport就有55條線路,與32bit 33.33MHz的PCI相比使用了更少的線路,可以8bit的HyperTransport確有1.6GB/Sec的數據傳輸能力,這就已經是PCI的 12倍了。HyperTransport使用的線路比PCI要少很多,也就是說功耗方面會更節約。效能高又省電是取代PCI系統的最大吸引力所在。

北橋依然使用EV6而和南橋和PCI等設備的連接完全采用效能高的HyperTransport

HyperTransport技術的現狀

除了可以使用在AMD的芯片組裡和CPU上之外,現在還有那些廠商會采用 HyperTransport??現在我們打聽的到消息只有Nvidia准備使用在自己開發的南橋芯片上,如果可以配合上2001年2月AMD宣布突出的北橋芯片的HyperTransport技術,那樣就可以一統原來PCI的天下,南北橋芯片完全具有全套高速的運行環境,那時真正的天下無敵,Hub Link、V-Link、DPI都被遠遠的甩在後面。Broadcom和SnadCraft也已經宣布會在自己的產品中加入HyperTransport 技術,而ALTERA公司在2001年第一季度都已經推出了符合HyperTransport標准的FPGA的可編程邏輯芯片。這一切太喜人了!

結論

HyperTransport只是用在電路基板上的技術,所以不會以擴展卡的形式出現,所以根本不會影響到現在PCI-X、Inifiband(用於系統外接設備的高速傳輸接口技術),而且HyperTransport只會老老實實的存在於系統內部,也不太可能用在數據存儲設備上,所以其它的行業沒有必要為此技術的產生而在恐慌什麼。

HyperTransport帶來的性能提升是可以肯定的,因為HyperTransport 還沒有完全的完善起來,一但成熟以後,這項技術將會是開放式的,由此可見它未來的前景是多麼的光明。HyperTransport在未來的日子不但會給很多開發設計商帶來新的開發資源,也為用戶提供了更快速的產品。開放式技術的還有一個優點就是價格是不計算在成本之內,那時我們拿到的 HyperTransport的產品都是低廉的。我們不得不贊歎這些無私的數字英雄們。

引用XDR 內存開發資料更新自述

XDR(eXtremeDataRate)內存是Rambus開發的一種高帶寬傳輸內存技術。SPARC處理器若加入此技術更能提供產品性能與競爭力。

引用HyperTransport Bus 更新自述

鑒於AMB、J-Bus、PCIE總線功能有限,特補上HyperTransport Bus以供參考。希望對你有用。

引用OpenSPARC T2 1.3 更新概述

A fully synthesizable, reduced footprint, System-level model has been developed, suitable for FPGA and Emulation Platforms. This model has single OpenSPARC T2 core, crossbar interconnect, and WISHBONE Memory Controller ( from www.opencores.org). This environment supports RTL Simulation, FPGA Synthesis and Gate-level simulation with a one-to-one correspondence (i.e a given test runs unchanged in the RTL Gate environments.) This environment is hardware platform neutral and can be ported on any FPGA prototyping board.

Specifically, following new flows are supported with this release:

* Added design compile-time flag 'FPGA'. Inclusion of this flag at the simulation or compile time will make design synthesizable with the FPGA tools. We have primarily tested this with Synplicity tool chain

* Added new regression environment in sims which allows full-system (core, crossbar, wishbone, memory controller) to be simulated in software.

* FPGA synthesis script 'fpga_synth' is provided to automate the synthesis of the design on FPGAs. Script is general enough to be used with any FPGA device or any vendor synthesis tool

* Finally, FPGA netlist simulation environment is provided to verify the functionality of the FPGA netlist

OpenSPARC 源代碼

[已通過安全檢測]RISING.ANTIVIRUS.Personal.Edition.2008.Retail

[病毒庫發布日期]2008-11-04

[已通過安裝測試]Windows XP Professional + Service Pack 3

共享服務時間:通常隨機

共享服務器:通常Razorback 3.1/Razorback 3.0

軟件版權歸原作者及原軟件公司所有 請遵循GPL授權協議使用

SPARC

Sun UltraSPARC II處理器

SPARC,全稱為“可擴充處理器架構”(Scalable Processor ARChitecture),是RISC微處理器架構之一。它最早於1985年由升陽電腦所設計,也是SPARC國際公司的注冊商標之一。這家公司於 1989年成立,其目的是向外界推廣SPARC,以及為該架構進行符合性測試。此外該公司為了擴闊SPARC設計的生態系統,SPARC國際也把標准開放,並授權予多間生產商采用,包括德州儀器、Cypress半導體、富士通等。由於SPARC架構也對外完全開放,因此也出現了完全開放原始碼的LEON 處理器,這款處理器以VHDL語言寫成,並采用LGPL授權。

SPARC架構原設計給工作站使用,及後應用在升陽、富士通等制造的大型SMP服務器上。而升陽開發的Solaris操作系統也是為SPARC設計的系統之一,除Solaris外,NeXTSTEP、Linux、FreeBSD、OpenBSD及NetBSD系統也提供SPARC版本。

現時最新版本的SPARC為第8及第9版,在2005年12月,升陽方面宣布其UltraSPARC T1處理器將采用開放原始碼方式。

開源CPU--OpenSparc T1簡介 FPGA級別

2006年3月,Sun宣布開源化其多核心UltraSparc T1 CPU的處理器設計,采用的是GNU通用公共許可證(GNU GPL license)。之前Sun已經公開了 Hypervisor API規范,允許各公司將Linux、BSD 及其他操作系統移植到UltraSparc T1平台。

Sun是業界首家將復雜的硬件設計使用GNU GPL許可進行發布的公司,而此舉也將為UltraSparc T1處理器增加曝光度,並吸引開發人員為該平台開發軟硬件解決方案。

該硬件設計的開源發布包括64-bit UltraSparc T1的Verilog硬件描述語言源代碼,驗證套裝和模擬模型,ISA規范及Solaris 10 OS虛擬鏡像。T1處理器的代號為“Niagara”,於去年發布並應用於Sun的T1000/T2000服務器中。 Sun目前推出了4、6、8核心的CPU版本,且每核心最多支持4線程,即總共最多32線程。T1基於Sparc V9架構,每核心集成16KB指令緩存和8KB主數據緩存,整個處理器共享3MB L2緩存。“OpenSparc T1”芯片設計,驗證套裝,架構和性能模型工具已經發布在http://www.opensparc.net網站。Sun還發布了“Cool Tools”,其中包括優化多線程CPU性能的各種程序以及CMT編程及描繪工具。

OpenSparc T1處理器的主要特征包括:

8個Sparc V9處理核心,每核心4線程,共計32線程

每處理核心16KB一級指令緩存,共128KB;

每處理核心8KB一級數據緩存,共64KB;

3MB二級緩存,4-way bank,12向關聯,各核心共享;

4個DDR2內存控制器,每通道位寬144bit,總帶寬峰值25GB/s;

IEEE754兼容浮點單元(FPU),各核心共享;

J-Bus輸入輸出接口,峰值帶寬2.56GB/s,128bit多元地址/數據復用總線。

UltraSPARC T1

Sun UltraSPARC T2解析

新一代的UltraSPARC T2處理器帶有8個核心,可以同時處理64個線程。T2的產品代號Niagra 2,不僅將應用在SUN自己的服務器上,還可能放在機頂盒、路由器等設備中。目前處理器由TI負責制造,采用SoC設計,帶有2個以太網接口,1個 PCIe ×8接口和4個雙通道FBDIMM內存控制器,整個處理器帶有5.03億個晶體管,核心大小342平方毫米,目前共推出1.2GHz與1.4GHz兩種頻率,在1.4GHz主頻的電壓為1.1伏,工作頻率上功耗85W。

UltraSPARC T2設計藍圖

65納米技術更節能

SUN已經成功將90納米的制作工藝成功轉制成65納米工藝,這樣意味著在同樣面積的芯片上可以放入更多的模塊。此外,T2還使用了其具有革命性的酷線程(CoolThreads?)芯片多線程技術(CMT)擴展到每線程功耗低於2瓦的UltraSPARC T2處理器。換句話說,擁有這項技術後,SUN的產品功耗將是競爭對手的十分之一或三十分之一。因此我們將看到業界功耗最低、8個內核、64個線程、4倍的吞吐量及網絡和安全的功能性於一身的產品。

芯片特點

處理器 八核心 工作主頻在900MHz – 1.4GHz

支持64線程

支持64 FB-DIMMs, 4個內存控制器

內存帶寬 60+GB/S

功耗 標准95W或最高123W

其他特點 8個浮點運算單元(FPUs)

雙10Gbit以太網接口和PCI-E支持

4MB二級緩存 (8 banks)

每核心1個安全協處理器

核心特點

核心特征 大小:12 mm2

8線程

2條指令管線 + 1個浮點計算 + 1個密碼加速單元

8KB 數據緩存+ 16KB 指令緩存

其他應用

其他應用 單插槽的機架或刀片服務器

WiMAX 無線

3G/4G

網絡基礎構架

性能翻倍,新一代架構有突破

UltraSPARC T2處理器將單一芯片上集成的系統功能提升到空前水平,在性能方面也是T1的兩倍。這首先要得益於它較高的吞吐量處理器能力,在 SPECint_rate2006和SPECfp_rate2006的測試中,這兩項成績分別是78.3 est和62.3 est,這主要得益於該處理器的8核和每核8線程的設計特色。在網絡連接方面,該處理器支持兩個可虛擬化的多線程的每秒10千兆比特的以太網端口,也就是萬兆以太網接口,並具有內建的包分類功能。在安全方面,8個密碼加速單元,一共有10個獨立的功能,可滿足不斷增長的安全需求,包括由NSA批准的算法,在性能上也沒有任何損失。

除此之外,在計算方面8個浮點單元,SUN將CMT的技術優勢擴展到了高性能計算領域,適用於各類科學應用,創立了單芯片 SPECfp_rate2006世界記錄和單芯片,有8條通道的輸入輸出接口可以滿足行業標准PCI Express I/O高速應用,如流媒體、數據庫讀/寫,以及數據備份等。4個內存控制器,提供了每秒50千兆字節以上的內存訪存速度。

以下表格中公布的是UltraSPARC T2單處理器的性能測試結果:

SPECint_rate2006 SPECfp_rate2006

1.4GHz Sun UltraSPARC T2 148% 134%

4.7GHz IBM POWER 6 115% 125%

2.66GHz Intel X5355 100% 100%

開源讓更多用戶受益

UltraSparc T2也將和UltraSparc T1一樣采用開放原始碼授權,到目前為止,OpenSPARC T1源碼的下載已經超過5,500次。現在Sun正准備將UltraSPARC T2的源碼在www.opensparc.net上向OpenSPARC社團發布。並且提供了程序員參考手冊、微架構技術規范、OpenSPARC T2β版評估項目等一系列措施,其中程序員參考手冊裡提供了軟件端口、操作系統端口,以及加快OpenSPARC T2項目進展的應用工具。微架構技術規范裡提供了對OpenSPARC T2硬件模塊特性和功能的詳細描述。OpenSPARC T2β版評估項目為一定數量的硬件設計人員和工具開發人員提供早期試用版,讓他們開始使用具有片上系統功能性的最新CMT技術。該項目將促進 OpenSPARC T2社團的發展,加快調試過程,以獲得性能更佳的OpenSPARC T2的第一個版本,配合具有海量線程特性的Solaris操作系統使高線程處理器UltraSPARC T2的技術優勢得到充分發揮,擁有開放的、低成本的虛擬化功能。

OpenSPARC Internals

This book is intended as a getting started companion to both OpenSPARC T1 and OpenSPARC T2. Now that Sun has open-sourced OpenSPARC T1 and T2, what can they be used for? One thing is certain: the real-world uses to which OpenSPARC will be put will be infinitely more diverse and interesting than anything that could be suggested in this book! OpenSPARC Internals was largely written by the team of OpenSPARC designers, developers, and programmers to acquaint readers with OpenSPARC and to guide users as they develop their own OpenSPARC designs. Here are some highlights of the book:

How to customize and use OpenSPARC

How to start using OpenSPARC code

How to make basic changes including

configuring number of cores or threads

paring to a smaller size

fitting on an FPGA

adding extensions

How to set up

simulation environment

emulation environment

How to verify an OpenSPARC design

OpenSPARC Internals

Edited by David Weaver

Published by Sun Microsytems, Inc.

369 pages

First printing, October 2008

ISBN 978-0-557-01974-8

What are they saying about OpenSPARC Internals?

The coverage is extremely broad and deep, from the basics of the OpenSPARC architecture, the rationale for throughput optimized microprocessor design, and the microarchitecture of the T1 and T2 implementations to a roadmap for using the T1 and T2 design database and design verification suites.

Kunle Olukotun

Stanford University

Professor, Electrical Engineering Computer Science

Founder, Afara Websystems

Director, Pervasive Parallelism Lab

OpenSPARC Internals provides an in-depth explanation of UltraSPARC T1/T2 internal architecture. It also serves as a detailed reference for guiding the implementation of a chip multithreaded microprocessor or the development of a SoC based application system. This book plays a significant role in helping promote not only the application of UltraSPARC T1/T2 but also the research and development of a chip multithreaded microprocessor as well as its applications.

Dongsheng Wang, Ph.D.

Tsinghua University, Beijing, China

Professor, Dept. of Computer Science

Director of Microprocessor and SoC Center

Like the open-source OpenSPARC T1 and T2 projects, OpenSPARC Internals delivers a comprehensive package. The book tells a complete story behind Sun's current flagship chip-multithreaded (CMT) processors-from the design theories and internals to the development tools and methodologies. The book is especially indispensable to anyone interested in uncovering ways to take advantage of the open-source OpenSPARC projects.

James C. Hoe

Carnegie Mellon University

Associate Professor, Electrical Computer Engineering

This book provides a wealth of practical tips for getting started using OpenSPARC, and OpenSPARC provides a great design to take full advantage of modern FPGAs.

Ivo Bolsens Chief Technology Officer, Xilinx Corporation

引用Simply RISC S1 Core

Written by Administrator

Monday 10 November 2008

Simply RISC S1 Core is a cutdown version of the OpenSPARC processor released as open-source by Sun Microsystems. The current version is based on the latest OpenSPARC T1 v1.6.

While OpenSPARC T1 (codename Niagara) features 8 SPARC CPU Cores and several peripherals, Simply RISC S1 Core (codename Sirocco) takes only one 64-bit SPARC Core from that design and adds a Wishbone/AMBA bridge and a simple reset controller:

Simply RISC S1

The whole process of designing a Wishbone bridge for the SPARC Core has been detailed in Chapter 11 of the book OpenSPARC Internals; the design now also supports an AMBA bridge as explained on the home page.

The enviroment contains scripts that support the use of three different flavors of the S1 Core; the following table summarizes the synthesis results obtained with Xilinx tools:S1 Core version Description Virtex-5 Area (*)

S1 Core EE Four threads, usual 16K+8K L1 caches 60K LUTs

S1 Core SE One thread, usual 16K+8K L1 caches 40K LUTs

S1 Core ME One thread, no L1 caches 37K LUTs

(*) Number of Slice LUTs on Virtex-5 devices, pre-Place-and-Route, obtained with provided push-button script

引用HyperTransport

HyperTransport技術是一種高速、低延時、點對點的連接,旨在提高電腦、服務器、嵌入式系統,以及網絡和電信設備的集成電路之間的通信速度。它的速度比某些現有技術高出48倍。

HyperTransport有助於減少系統之中的布線數量,從而能夠減少系統瓶頸,讓當前速度更快的微處理器能夠更加有效地在高端多處理器系統中使用系統內存。

HyperTransport技術的設計目的是:

提供比現有技術高得多的帶寬

使用低延時響應和較少的引腳數

在保持與傳統電腦總線的兼容性的同時,可以擴展到新的SNA(系統網絡架構)總線

對操作系統保持透明,對周邊設備驅動程序的影響極小

HyperTransport技術由AMD和眾多行業合作伙伴共同開發而成,由 HyperTransport技術聯盟(一家位於得克薩斯的非盈利性企業)管理和發放許可。如需查看關於HyperTransport的全部規格和更多信息,請訪問HyperTransport.org。

HyperTransport雙向傳輸總線技術,相對於過去的PCI總線設計而言,Hyper Transport技術從根本上有了顯著的提高。從單純的數據比較來看,Hyper Transport在數據傳輸率上達到了驚人的12.8GB/s,這個數值相比Intel最新3GIO技術的最初理論傳輸率高出了很多(3GIO早期產品的帶寬設計為2.5GB/s,遠景規劃為10GB/s)。同目前的PCI總線而言,HyperTransport的數據傳輸率高出了整整96倍以上

HyperTransport最初是AMD在1999年提出的一種總線技術,隨著AMD64位平台的發布和推廣,HyperTransport應用越來越廣泛,也越來越被人們所熟知。

HyperTransport是一種為主板上的集成電路互連而設計的端到端總線技術,它可以在內存控制器、磁盤控制器以及PCI總線控制器之間提供更高的數據傳輸帶寬。HyperTransport采用類似DDR的工作方式,在400MHz工作頻率下,相當於800MHz的傳輸頻率。此外HyperTransport是在同一個總線中模擬出兩個獨立數據鏈進行點對點數據雙向傳輸,因此理論上最大傳輸速率可以視為翻倍,具有4、8、16及32位頻寬的高速序列連接功能。在400MHz下,雙向4bit模式的總線帶寬為0.8GB/sec,雙向 8bit模式的總線帶寬為1.6GB/sec;800MHz下,雙向8bit模式的總線帶寬為3.2GB/sec,雙向16bit模式的總線帶寬為 6.4GB/sec,雙向32bit模式的總線帶寬為12.8GB/sec。以400MHz下,雙向4bit模式為例,帶寬計算方法為 400MHz×2×2×4bit÷8=0.8GB/sec。

HyperTransport還有一大特色,就是當數據位寬並非32bit時,可以分批傳輸數據來達到與32bit相同的效果。例如16bit的數據就可以分兩批傳輸,8bit的數據就可以分四批傳輸,這種數據分包傳輸的方法,給了 HyperTransport在應用上更大的彈性空間。

2004年2月,HyperTransport技術聯盟(Hyper Transport Technology Consortium)又正式發布了HyperTransport 2.0規格,由於采用了Dual-data技術,使頻率成功提升到了1.0GHz、1.2GHz和1.4GHz,數據傳輸帶寬由每通道1.6Gb/sec 提升到了2.0GB/sec、2.4Gb/sec和2.8GB/sec,最大帶寬由原來的12.8Gb/sec提升到了22.4GB/sec。

當HyperTransport應用於內存控制器時,其實也就類似於傳統的前端總線(FSB,Front Side Bus),因此對於將HyperTransport技術用於內存控制器的CPU來說,其HyperTransport的頻率也就相當於前端總線的頻率。

******************************************

為什麼才會誕生HyperTransport

Intel從82810芯片組開始,創造了自己的Hub Link技術來連接南北橋芯片,使得當時810芯片組成為最能發揮Ultra DMA66傳輸性能的芯片組。因為Intel的授權費用高昂,所以很多的台灣芯片組廠商為了不向Intel取得Hub Link (8bit,133Mhz,266MB/Sec)技術授權。為了彌補在性能上可能產生的劣勢,芯片組廠商都開發自己的技術來解決這一問題。例如VIA開發了V-Link(32bit,66Mhz,266MB/Sec),SIS也開發了他們自己的DPI(Dedicated Pci to Ide bus,266MB/Sec)或者是最新的Multi-threaded IO Link(1.2GB/Sec)。

AMD也同樣針對自己的CPU設計有支持的芯片組,他們同樣必須面對如何連接南北橋才能更好的發揮Ultra DMA 66/100的效能問題。AMD的技術絕對可以達到這個水平,但是AMD的目的是不想開發獨自一家的芯片組技術,而是想制訂出一種能適用於各種高速度芯片組之間的傳輸界面,這就是LDT (Lightning Data Transport),2001年2月改名為HyperTransport。

HyperTransport的發展之路

HyperTransport的前身稱為LDT,最早在99年的MicroProcessor Forum就提出了這個高速傳輸接口界面,當時是同 SiedgeHammer CPU一同提出的。不過當時的LDT技術幾乎就只能說純粹是個想法而已,一直到2000年5月份的時候,才正式推出了它的1.0版,有了運行規格,但當時沒有完成任何電氣規格方面的設計,只是到了目前才完善了電氣規格方面的制定(目前為1。01C版本,需要通過AMD的授權才能正式獲得。)

在2000 WinHEC上,AMD再次將LDT技術搬上講壇,據說當時有1500個廠商代表出席參加,整個會場爆滿。然後開始有了HyperTransport的技術白皮書。之後的2000年6月Platform 2000技術會議上AMD再次將LDT技術,擺上桌面。人們一次次接觸到這項新技術,越發感興趣,加上優秀的性能,很大程度上促進了 HyperTransport技術的發展。

HyperTransport技術概要

HyperTransport除了可以將芯片間數據的高速傳輸之外,它還具有 封包傳輸技術(Packet-Based) 、 雙條單向數據流及點對點的數據連接方式 、 彈性數據帶寬 等。使用HyperTransport自然是有它的道理的,它的可以改善系統數據傳輸的瓶頸,可以為系統設計人員制造更高效能的系統設備提供基礎,完完全全的加快整個系統性能運行效能,好處可以說是接踵而來。 HyperTransport到底有多快呢?峰值可以達到6.4GB/Sec,就拿現在的Hub Link、V-Link,DPI等技術來看,HyperTransport是他們的24倍,對於32bit、33.33Mhz的PCI相比,是PCI的 48倍。看到這裡我想你已經很明白我們為什麼要HyperTransport技術啦!

那些設備可能要用到HyperTransport技術

既然HyperTransport技術帶來性能的提升如此之高,那麼那些系統會需要高速數據交流和高速芯片組呢?

1、 網絡路由器

2、 網絡交換機

3、 網絡集線器

4、 服務器

5、 工作站

除了這些設備,本人覺得還不完善。在個人的設備和家庭設備上也完全可以使用。未來的手持通訊設備、家庭計算機網絡設備等,都是HyperTransport技術可以完全發揮作用的地方。

HyperTransport技術對於網絡傳輸方面的性能提高

現在的網絡設計簡直就是為了自身服務器能力的高效時代,所有的設備都需要高檔。就連Intel 方面的Pentium 4都自稱 NetBurst 運算構架,特別強調對於網絡方面有性能的提高。同樣在AMD方面也有HyperTransport的數據處理技術,也是同樣大力宣傳對網絡系統可以帶來非常之大的宣傳。因為現在的環境是這樣,只有這樣才能吸引人。HyperTransport對與網絡方面的幫助,主要在於電腦系統同網絡設備同時才用HyperTransport技術時,才可能得到非常高效的性能提高。其中包括WEB服務器使用的HyperTransport、寬帶網絡數據設備的HyperTransport、TCP-IP交換機使用的HyperTransport、防火牆使用的HyperTransport、工作站使用的HyperTransport、打印系統使用的HyperTransport、桌面電腦使用的HyperTransport等等。所有的硬件系統都用上HyperTransport的技術,自然而然網絡速度方面也會有一個飛越。

HyperTransport的技術合作伙伴

HyperTransport不僅僅對電腦效能方面有幫助,在網絡設備和通訊設備方面都有很高的性能提高。對於提出這一技術的AMD自身來說,至少有兩個地方可以使用到HyperTransport:

AMD的芯片組

在過去的年代裡南北橋芯片組以33bit、33MHz的PCI界面連接,但是隨著UDMA 66/100的傳輸技術出現後,不足以應付這些資料的傳輸速度。現在HyperTransport出現後,完全可以取代PCI,而且足以應付PCI-X、 66.66MHz PCI都游仞有余。

AMD的多處理器架構

從Athlon開始就可以支持多處理器運行的架構,但是AMD現在使用的EV6匯排流總線似乎難以應付大容量數據的處理,為了未來的K8或者更強大的處理器多顆並行使用的時候,如果使用HyperTransport接口來做數據資料的傳輸,你可以想象帶寬所帶來的性能提高。

其他更多的廠商

其實在其它系統上有100多家的廠商和AMD在共同研究、討論和推廣HyperTransport。其中有代表性的為一下幾家:

Cisco 路由器、交換機

Sun 服務器、工作站、

Via 處理器、芯片組、顯示芯片、其它芯片

Sis 芯片組、顯示芯片、其它芯片

Ali 芯片組、其它芯片

AMP 網絡連接器和接插件

Broadcom 寬帶網絡控制芯片

Phoenix BIOS、硬件底層程序

Fujitsu PC個人機、激光打印機、MO、硬盤

TYAN 主板、PC個人機

Nvidia 芯片組、顯示芯片、多媒體芯片

Ati 芯片組、顯示芯片、多媒體芯片

ALTERA 邏輯程控芯片

HyperTransport的運行規格

HyperTransport最吸引人的地方在那裡,就是在於那6.4GB的高速傳輸速度。 HyperTransport是由兩條點對點的單向數據傳輸路徑組成(一條為輸入、一條為輸出)。兩條單向傳輸路徑的數據帶寬是可以根據數據量的大小而彈性改變,最低的有2bit,可以調節為4bit、8bit、16bit、32bit,HyperTransport的運行在400MHZ的時鐘頻率下,但是使用的是DDR SDRAM相同的雙鐘頻觸發技術,所以在400MHZ的額定頻率下,其實是相當與工作在800MHZ的效能,正是如此每個數據的資料傳輸路徑最高可以有 800Mb/Sec。如果這樣來計算,當輸入輸出的資料輸出路徑都設置到最高的32bit時,然後以全速度400MHz DDR(相當於800MHZ)的時鐘頻率運行,這時數據最高的傳輸率就出現了---6.4GB/Sec。但是當傳輸的數據路徑的數據寬度降低為非 32bit,那麼傳輸數據的速度也自然下降。不過HyperTransport還有一大特色就是當數據資料寬度為非32bit (4byte)時,可以分批傳輸數據來達到32bit相同的效果,比如說16bit的數據就分兩批傳輸,在使用8bit數據時就分4批傳送,這種分包傳輸數據的方法,給了HyperTransport更大的彈性空間,最小4byte,最大64byte。對於資料快速傳輸帶來了很大的形式上的改良,提高了系統數據處理性能。

HyperTransport與其它系統接口界面速度比較

接口界面 峰值資料傳輸速度

PCI(32bit 33.33MHz) 132MB/Sec

PCI(64bit 66.66MHz) 528MB/Sec

PCI-X 1GB/Sec

InifiBand 4GB/Sec

HyperTransport 6.4GB/Sec

HyperTransport的電氣規格

HyperTransport采用的是所謂的差動式數據傳輸,這於Ultra SCSI/2 LVD或者USB數據傳輸方式是相同的,既每個bit都是用兩條傳輸線的電壓之間的差異來傳輸數字信號,當A線路的電壓電位高於B線路時,看做 1 ,反之為 0 。高速數據傳輸的特點通常是要使用非常之低的運行電壓,對於HyperTransport來說這點也是十分正確的。 HyperTransport的運行電壓為1.2V,電壓可以接受的差異標准是正負5%(差異600mV),換句話說來說就是在1.26-1.14V之間都是可以接受正確邏輯傳輸信號,這是針對信息發送方面的定義,在數據接收方面則為200mV的電壓差異。可見HyperTransport傳輸的偏差允許還是比較大的。同SCSI和IDE的規范相同,HyperTransport也需要在傳輸路徑中要有終端電阻,但是只要100歐姆的電阻即可,大大減低了電阻的成本。而且在采用HyperTransport的主板上,只要設計的線路不要超過24英寸,就能保證先前提到的800Mbit/Sec的數據傳輸率。

用HyperTransport取代PCI

AMD決定用HyperTransport用在自家的芯片組上來取代使用已久的PCI。既然如此應該有超越PCI的地方,對此AMD做了專門的解釋。下圖就是它的數據處理規格。(圖Hypertech4.bmp)我們都是知道 HyperTransport是每一個數據有是有2個資料線路來傳輸數據的,也就是說每bit就擁有2條傳輸資料的線路,上圖給出了各種信號的線路,大家自己相加一下就知道可以使用多少線路。當8bit的HyperTransport就有55條線路,與32bit 33.33MHz的PCI相比使用了更少的線路,可以8bit的HyperTransport確有1.6GB/Sec的數據傳輸能力,這就已經是PCI的 12倍了。HyperTransport使用的線路比PCI要少很多,也就是說功耗方面會更節約。效能高又省電是取代PCI系統的最大吸引力所在。

北橋依然使用EV6而和南橋和PCI等設備的連接完全采用效能高的HyperTransport

HyperTransport技術的現狀

除了可以使用在AMD的芯片組裡和CPU上之外,現在還有那些廠商會采用 HyperTransport??現在我們打聽的到消息只有Nvidia准備使用在自己開發的南橋芯片上,如果可以配合上2001年2月AMD宣布突出的北橋芯片的HyperTransport技術,那樣就可以一統原來PCI的天下,南北橋芯片完全具有全套高速的運行環境,那時真正的天下無敵,Hub Link、V-Link、DPI都被遠遠的甩在後面。Broadcom和SnadCraft也已經宣布會在自己的產品中加入HyperTransport 技術,而ALTERA公司在2001年第一季度都已經推出了符合HyperTransport標准的FPGA的可編程邏輯芯片。這一切太喜人了!

結論

HyperTransport只是用在電路基板上的技術,所以不會以擴展卡的形式出現,所以根本不會影響到現在PCI-X、Inifiband(用於系統外接設備的高速傳輸接口技術),而且HyperTransport只會老老實實的存在於系統內部,也不太可能用在數據存儲設備上,所以其它的行業沒有必要為此技術的產生而在恐慌什麼。

HyperTransport帶來的性能提升是可以肯定的,因為HyperTransport 還沒有完全的完善起來,一但成熟以後,這項技術將會是開放式的,由此可見它未來的前景是多麼的光明。HyperTransport在未來的日子不但會給很多開發設計商帶來新的開發資源,也為用戶提供了更快速的產品。開放式技術的還有一個優點就是價格是不計算在成本之內,那時我們拿到的 HyperTransport的產品都是低廉的。我們不得不贊歎這些無私的數字英雄們。

- 上一頁:《REALbasic 2008 Release 4.2專業版》(REALbasic Professional 2008 Release 4.2)4.2 pro[壓縮包],編程開發、資源下載

- 下一頁:《tomcat6》(tomcat6),編程開發、資源下載

相關資源:

- [系統工具]《U盤變內存》(eBoostr Pro)V4.0.build.544 破解版[壓縮包]

- [操作系統]《FreeBSD5.4最新完全安裝版》(FreeBSD

- [軟件綜合]《音效編輯軟件》(audacity for veket)2.0.3 中文版[安裝包]

- [網絡軟件]《谷歌浏覽器》(Chrome for veket)28 開發版[安裝包]

- [應用軟件]《Xilisoft.AVI.to.SWF.轉換v5.1.26.1030注冊版》(Xilisoft.AVI.to.SWF.Converter.v5.1.26.1030.Incl.Keygen-Lz0)v

- [多媒體類]《虛擬聲音環境設計套件》(VRSonic VibeStudio Designer )v2.9.0[壓縮包]

- [應用軟件]《開放源碼的辦公套件》(Libreoffice)3.3.2[安裝包]

- [應用軟件]《Mac平台虛擬機Parallels正式版》(Parallels Desktop for Mac)Parallels Desktop for Mac 3186,應用軟件、資源下載

- [多媒體類]《視頻圖像合成/處理特效插件》(Boris Continuum Complete )v8.0 for CS3 CS4 CS5 CS5.5[壓縮包]

- [多媒體類]AE插件純淨版

- [生活圖書]《我家的手工茶點》掃描版[PDF]

- [學習課件]《練功與養生》掃描版[PDF]資料下載

- [生活圖書]《少林八段錦圖解》掃描版[PDF]

- [應用軟件]《名片制作軟件》(My Professional Business Cards)(5.0)[Bin],應用軟件、資源下載

- [小說圖書][電子小說]盜墓筆記TXT全集小說 盜墓筆記txt(1-8)真正完整版大結局

- [多媒體類]《視頻剪輯軟件》(AVS Video ReMaker)v4.0.7.139[壓縮包]

- [應用軟件]《CCNP實驗模擬器》(Boson NetSim)Beta3,應用軟件、資源下載

- [生活圖書]《教你找到好工作》掃描版[PDF]

- [硬盤游戲]《海商王》(Port Royale)繁體中文硬盤版[v1.4.0.3][壓縮包]

- [光盤游戲]《美國隊長》(Captain America)[59-vol.6+Annuals/連載中][漫畫]全彩英文版[壓縮包]

- 《摩托羅拉手機配套工具 合集》(Motorola Mobile Phone Tool collections)V3.11H,4.0,4.1[光盤鏡像],行業軟件、資源下載

- 《安裝制作軟件 9.0》(InstallAware Studio Admin v9.0)[光盤鏡像],編程開發、資源下載

- SSS論壇易語言快速入門培訓

- 《Emurasoft文本編輯器》(Emurasoft EmEditor Professional)v9.17 簡體中文漢化版[安裝包]

- 《MATLAB®

- 《Perl程序開發》(ActiveState Perl Dev Kit Pro)v9.1.1.295479/x86+x64/含注冊機+授權文件[壓縮包]

- 《J2EE集成開發環境Blue版》(MyEclipse Blue Edition)7.5[安裝包],編程開發、資源下載

- 《IBM Rational Robot》(IBM Rational Robot)V 7.0,編程開發、資源下載

- 《英特爾® C++ 編譯器 》(Intel CPP Compiler Professional )v11.1.058 MACOSX

- 《C語言開發系統》(CoDeveloper Pro Universal )V3.50b3 [壓縮包]

- 《MySQL中文增強版 2.0 RC1》(MySQL Chinese+ 2.0 RC1)Release Candidate 1,編程開發、資源下載

- 《XML開發工具()》(stylus

免責聲明:本網站內容收集於互聯網,本站不承擔任何由於內容的合法性及健康性所引起的爭議和法律責任。如果侵犯了你的權益,請通知我們,我們會及時刪除相關內容,謝謝合作! 聯系信箱:[email protected]

Copyright © 電驢下載基地 All Rights Reserved